Nºd'ordre NNT : 2020LYSEI107

# THÈSE de DOCTORAT DE L'UNI VERSI TÉ DE LYON opérée au sein de l'Institut National des Sciences Appliquées de Lyon

École Doctorale N° ED162 MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE

Spécialité de doctorat : Génie Mécanique

Soutenue publiquement le 01/12/2020 par : Louise CARTON

Mechanical properties of thin silicon wafers for photovoltaic applications: influence of material quality and sawing process

Devant le jury composé de :

SCHOENFELDER Stephan PAGGI Marco GUILLEMOLES Jean-François NELIAS Daniel **RIVA** Roland FOURMEAU Marion MEHL Céline

Professeur des universités HTWK Leipzig Professeur des universités Directeur de recherche Professeur des universités INSA Lyon Ingénieur chercheur Maître de conférences Ingénieure

IMT Lucca CNRS CEA-INES INSA Lyon ADEME

Rapporteur Rapporteur Président Directeur de thèse Co-directeur Co-encadrante Invitée

### Département FEDORA- INSA Lyon - Ecoles Doctorales - Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                                             | NOMET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIMIE    | CHIMIE DE LYON<br>http://www.edchimie-lyon.fr<br>Sec. : Renée EL MELHEM<br>Bât. Blaise PASCAL, 3e étage<br>secretariat@edchimie-lyon.fr<br>INSA : R. GOURDON                                                                | M. Stéphane DANIELE<br>Institut de recherches sur la catalyse et l'environnement de Lyon<br>IRCELYON-UMR 5256<br>Équipe CDFA<br>2 Avenue Albert EINSTEIN<br>69 626 Villeurbanne CEDEX<br>directeur@edchimie-lyon.fr                                                                                              |

| E.E.A.    | <u>ÉLEC TRO NIQUE,</u><br><u>ÉLEC TRO TEC HNIQUE,</u><br><u>AUTO MATIQUE</u><br>http://edeea.ec-lyon.fr<br>Sec. : M.C. HAVGOUDOUKIAN<br>ecole-doctorale.eea@ec-lyon.fr                                                      | M. Gérard SCO RLETII<br>École Centrale de Lyon<br>36 Avenue Guy DE COLLONGUE<br>69 134 Écully<br>Tél: 04.72.18.60.97 Fax 04.78.43.37.17<br>gerard.scorletti @ec-lyon.fr                                                                                                                                          |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME,<br>MICROBIOLOGIE, MODÉLISATION<br>http://e2m2.universite-lyon.fr<br>Sec. : Sylvie ROBERJOT<br>Bât. Atrium, UCB Lyon 1<br>Tél : 04.72.44.83.62<br>INSA : H. CHARLES<br>secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND<br>UMR 5557 Lab. d'Ecologie Microbienne<br>Université Claude Bernard Lyon 1<br>Bâtiment Mendel<br>43, boulevard du 11 Novembre 1918<br>69 622 Villeurbanne CEDEX<br>philippe.normand@univ-lyon1.fr                                                                                           |

| EDISS     | INTERDIS CIPLINAIRE<br>SCIENCES-SANTÉ<br>http://www.ediss-lyon.fr<br>Sec. : Sylvie ROBERJOT<br>Bât. Atrium, UCB Lyon 1<br>Tél : 04.72.44.83.62<br>INSA : M. LAGARDE<br>secretariat.ediss@univ-lyon1.fr                      | Mme Sylvie RICARD-BLUM<br>Institut de Chimie et Biochimie Moléculaires et Supramoléculaires<br>(ICBMS) - UMR 5246 CNRS - Université Lyon 1<br>Bâtiment Curien - 3ème étage Nord<br>43 Boulevard du 11 novembre 1918<br>69622 Villeurbanne Cedex<br>Tel : +33(0)4 72 44 82 32<br>sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFO RMATIQ UE ET<br>MATHÉMATIQ UES<br>http://edinfomaths.universite-lyon.fr<br>Sec. : Renée EL MELHEM<br>Bât. Blaise PASCAL, 3e étage<br>Tél : 04.72.43.80.46<br>infomaths@univ-lyon1.fr                                   | M. Hamamache KHEDDO UCI<br>Bât. Nautibus<br>43, Boulevard du 11 novembre 1918<br>69 622 Villeurbanne Cedex France<br>Tel: 04.72.44.83.69<br>hamamache.kheddouci@univ-lyon1.fr                                                                                                                                    |

| Matériaux | MATÉRIAUX DE LYON<br>http://ed34.universite-lyon.fr<br>Sec. : Stéphanie CAUVIN<br>Tél : 04.72.43.71.70<br>Bât. Direction<br>ed.materiaux@insa-lyon.fr                                                                       | M. Jean-Yves BUFFIÈRE<br>INSA de Lyon<br>MATEIS - Bât. Saint-Exupéry<br>7 Avenue Jean CAPELLE<br>69 621 Villeurbanne CEDEX<br>Tél: 04.72.43.71.70 Fax: 04.72.43.85.28<br>jean-yves.buffiere@insa-lyon.fr                                                                                                         |

| M EGA     | MÉCANIQUE, ÉNERGÉTIQUE,<br>GÉNIE CIVIL, ACOUSTIQUE<br>http://edmega.universite-lyon.fr<br>Sec. : Stéphanie CAUVIN<br>Tél : 04.72.43.71.70<br>Bât. Direction<br>mega@insa-lyon.fr                                            | M. Jocelyn BONJOUR<br>INSA de Lyon<br>Laboratoire CETHIL<br>Bâtiment Sadi-Carnot<br>9, rue de la Physique<br>69 621 Villeurbanne CEDEX<br>jocelyn.bonjour@insa-lyon.fr                                                                                                                                           |

| ScSo      | ScSo*<br>http://ed483.univ-lyon2.fr<br>Sec. : Véronique GUICHARD<br>INSA : J.Y. TOUSSAINT<br>Tél : 04.78.69.72.76<br>veronique.cervantes@univ-lyon2.fr                                                                      | M. Christian MONTES<br>Université Lyon 2<br>86 Rue Pasteur<br>69 365 Lyon CEDEX 07<br>christian.montes@univ-lyon2.fr                                                                                                                                                                                             |

\*ScSo: Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

Cette thèse est accessible à l'adresse : http://theses.insa-Iyon.fr/publication/2020LYSEI107/these.pdf © [L. Carton], [2020], INSA Lyon, tous droits réservés

# Abstract

Crystalline silicon is the key material of photovoltaic technology: over 95 % of solar cells use thin silicon slices as base substrates. These so-called wafers are obtained by wire sawing of the solid bricks, a step which accounts for a significant portion of the total photovoltaic module cost. A better use of silicon material is therefore a privileged pathway towards significant reduction of the solar energy production costs, thereby enabling a sustainable and rapid growth. In practice, enhancing material yield implies reducing wafer as -cut thickness as well as the diameter of the cutting wires. Nevertheless, silicon remains a brittle crack-sensitive material and the increase in breakage rates when handling these thin wafers is a major obstacle to the economic benefit. In this context, it is essential to improve our understanding of the mechanisms responsible for wafer embrittlement and failure. Only in this way will we be able to establish recommendations for the manufacturing of silicon wafers, as well as to propose adjusted handling technologies.

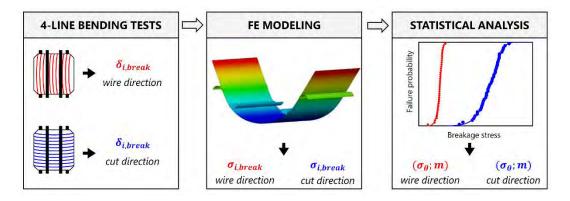

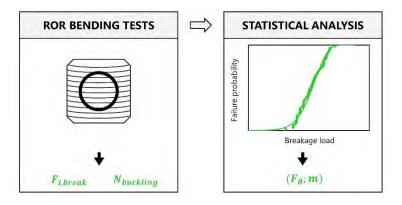

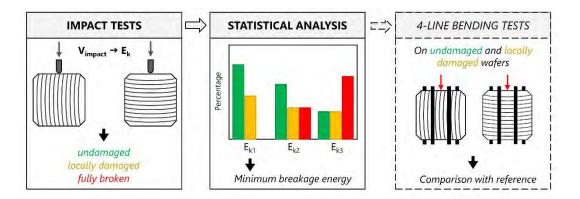

This work investigates the mechanical properties of silicon wafers obtained using diamond wire sawing. We developed a mechanical characterization methodology suited for these thin, brittle samples, combining destructive 4-line and biaxial bending tests with dynamic impacts. This methodology was applied on more than 7 000 wafers sawn in our laboratory equipment using known and controlled parameters. Jointly, finite element simulations were implemented to better understand the underlying phenomena. In parallel, we characterized the properties of the as-cut wafer surface using topology and microscopy (optical, confocal, scanning electron) techniques, as well as through evaluation of microcracks depth.

With the ambition to understand which of the typical defects present in a silicon wafer are the most critical regarding mechanical failure, we implemented an original procedure to isolate their respective influence. The results obtained disprove the commonly accepted fact that edge defects are the main origin of failure, and show that the most dangerous mechanical damage is located in a thin subsurface layer (< 3  $\mu$ m), which is generated during the sawing step. By coupling 4-line bending and dynamic tests on wafers of different as-cut thicknesses (from 180 to 100  $\mu$ m), we demonstrated that thinner wafers exhibit an increased bending flexibility without alteration of their intrinsic mechanical strength (failure stress), accompanied however by a higher risk of failure following an edge impact. Through 4-line bending tests on samples obtained from bricks of different crystallinity sawn using identical conditions, we highlighted that the presence of structural defects in multicrystalline and mono-like silicon is indirectly responsible for the lower fracture strength of the wafers. The increased suffering of the diamond wire when cutting through these defects generated indeed deeper microcracks than on the monocrystalline samples. Finally, through a design of experiment approach, we show that the characteristics of the diamond wire play a more important role on the mechanical properties of the resulting wafers than the parameters of the sawing process.

**KEYWORDS:** photovoltaic solar cell, silicon wafer, diamond wire sawing, mechanical strength, fracture, subsurface damage, TTV, 4-line bending, Ring on Ring, impact tests

- i -

# Résumé

Le silicium cristallin est le matériau clé de la technologie photovoltaïque : plus de 95 % des cellules solaires sont élaborées à partir de tranches fines de silicium. Ces wafers sont obtenus par découpe au fil diamanté de briques, étape qui représente une part significative du coût final du module photovoltaïque. Une meilleure utilisation du matériau silicium constitue alors une piste privilégiée pour diminuer significativement les coûts de production d'électricité photovoltaïque, et permettre ainsi de maintenir une croissance élevée et durable. En pratique, l'amélioration de ce rendement matière passe par une diminution de l'épaisseur des wafers et du diamètre des fils de découpe. Néanmoins, le silicium reste un matériau fragile sensible à la fissuration, et l'augmentation des taux de casse de ces substrats fins durant les étapes de manipulation constitue un obstacle majeur au gain économique potentiel. Dans ce contexte, il est primordial d'améliorer notre compréhension des mécanismes de rupture et de fragilisation des wafers. C'est à cette condition que nous pourrons établir des recommandations sur la fabrication et la mise en forme du silicium, ainsi que proposer des techniques de manipulation adéquates.

Ce travail de thèse étudie les propriétés mécaniques des wafers de silicium obtenus par découpe au fil diamanté. Nous avons développé une méthodologie de caractérisation mécanique adaptée à la fragilité de ces échantillons, en combinant des essais de rupture de flexion 4-lignes et biaxiale, ainsi que des sollicitations dynamiques par chocs. Cette méthodologie a pu être appliquée à plus de 7 000 wafers découpés dans notre scie de laboratoire avec des conditions et paramètres connus. Conjointement, des simulations numériques par la méthode des éléments finis ont permis de mieux comprendre les phénomènes mis en jeux. En parallèle, nous avons caractérisé les propriétés de la surface brute de découpe des wafers au moyen de techniques de topologie, de microscopie (optique, confocale, électronique à balayage) et d'évaluation de la profondeur de microfissures.

Avec l'ambition de comprendre quels défauts typiques d'un wafer de silicium sont les plus critiques pour sa défaillance mécanique, nous avons mis en place une procédure originale consistant à isoler leur influence respective. Les résultats obtenus infirment l'hypothèse communément admise selon laquelle les défauts de bords sont la principale source de rupture, et démontrent que l'endommagement le plus dangereux se situe dans une couche de faible épaisseur (< 3 µm) sous la surface, générée lors de l'étape de découpe. En couplant des tests de flexion avec des essais dynamiques sur des wafers de différentes épaisseurs (de 180 à 100 µm), nous avons montré que l'amincissement des plaquettes permet un gain de flexibilité sans diminution de la résistance mécanique intrinsèque (contrainte à rupture), mais qui s'accompagne d'un risque plus élevé de ruine suite à un impact sur la tranche. Au travers d'essais de flexion 4 lignes sur des échantillons issus de brigues de cristallinité différentes mais découpés dans les mêmes conditions, nous avons mis en évidence que l'existence de défauts structurels dans le silicium multicristallin et mono-like est indirectement responsables de la diminution de la résistance à rupture des wafers. En effet, la difficulté accrue du fil à traverser ces défauts se traduit par des microfissures plus profondes que dans les échantillons monocristallins. Enfin, une approche par plans d'expérience nous permet de comprendre que les caractéristiques du fil diamanté utilisé jouent un rôle plus important sur les propriétés mécaniques des wafers obtenus que les paramètres du procédé de découpe.

**MOTS-CLÉS** : cellule solaire photovoltaïque, wafer de silicium, découpe au fil diamanté, résistance mécanique, rupture, endommagement de subsurface, TTV, flexion 4-lignes, flexion Ring on Ring, essais de chocs

# Dedication

A ma famille

Maman et papa, pour n'avoir jamais douté de ce dont j'étais capable

Violette et Jules, pour votre rageuse et contagieuse envie d'un monde plus juste

\*\* Pour ce qui est de l'avenir, il ne s'agit pas de le prévoir, mais de le rendre possible \*\*

Antoine de Saint Exupéry *Citadelle*, 1948

# Acknowledgments

Ce travail de thèse n'aurait jamais pu aboutir sans le soutien quotidien ou ponctuel de nombreuses personnes qui m'ont entourées pendant ces trois années. Au terme de cette aventure, je souhaite leur exprimer ma plus profonde et sincère reconnaissance.

J'aimerais commencer par remercier l'ADEME, pour son financement sans lequel cette thèse n'aurait probablement pas vu le jour, bien sûr, mais pas uniquement. Je suis avant tout très reconnaissante d'avoir pu rejoindre une communauté incroyable de doctorants issus de domaines très différents, mais partageant l'envie de contribuer à un meilleur futur au travers de leur travail de recherche. Je garde un souvenir enrichissant de tous les moments d'échange partagés avec eux, notamment au cours de deux éditions de JDD, échanges qui constituent selon moi un point fort d'une thèse ADEME. J'adresse également un remerciement tout particulier à Céline Mehl, pour son suivi bienveillant au cours de ces trois années.

I would like to express my deepest gratitude to Stephan Schoenfelder, Marco Paggi and Jean-François Guillemoles for agreeing to be part of my PhD committee. Thank you for the time spent reading my manuscript and for your constructive feedback. It has been a pleasure and honor to discuss my work with you during the defense.

Cette thèse ne serait jamais arrivée au bout sans une équipe d'encadrement aux petits oignons. Merci à Daniel Nélias, Roland Riva, et Marion Fourmeau, trio complémentaire qui a guidé mon travail du premier au dernier jour de thèse. Vous avez su m'accorder la liberté et l'autonomie nécessaires pour explorer ce sujet à fond et à ma manière, mais aussi être rassurants dans les moments où je ne savais plus trop où j'en étais ni où j'allais. J'ai beaucoup appris à vos côtés, et je garderai un souvenir précieux de notre collaboration.

Il me faut aussi adresser un immense remerciement à toute l'équipe de découpe du laboratoire LMPS : Fabrice Coustier, pour ton expertise sans limite du sciage diamant et tes idées pour des découpes toujours plus farfelues. Nicolas Velet, pour des heures passées à soigneusement nettoyer et trier des wafers, tout ça pour que je les casse après. Amal Chabli, pour la tornade d'énergie que tu ramènes dans toutes les discussions auxquelles tu participes.

Je souhaite aussi remercier tous les autres membres du LMPS ayant participé à ce travail. Merci à Sylvain Rousseau pour les nombreuses attaques chimiques à Restaure, surtout les plus exotiques (on n'oubliera jamais ce scotch se dissolvant doucement dans le bac de solution ...). Merci à Virginie Brizé pour la tâche ingrate et minutieuse de polissage des bords des wafers. Merci à Nelly Plassat pour les découpes laser sur mes plaquettes.

Plus généralement, j'adresse toute ma gratitude à la bonne ambiance du laboratoire LMPS dans son ensemble. Merci pour votre bonne humeur, pour tous les événements off, du repas de Noël aux examens de meilleur ouvrier de France en restauration - vous avez fait de ces trois ans une aventure humaine, malgré les circonstances particulières sur la fin de cette thèse. Je ne peux m'empêcher d'être émue en songeant que très bientôt, le LMPS tel que je l'ai connu disparaîtra : n'oubliez surtout pas d'emmener un peu de vous partout où vous atterrirez.

Ce travail a aussi trouvé de l'aide en dehors de notre laboratoire. Je tiens à remercier Nicolas Enjalbert pour toujours plus d'attaques chimiques, Jean-Marc Fabbri de la plateforme PFNC de Grenoble pour sa patience avec la polisseuse, et Olivier Sicardy pour les mesures de diffraction aux rayons X. J'aimerais aussi remercier tous les « non-permanents » (cette si jolie désignation !) de l'INES. Stagiaires, thésards, alternants et CDD avec qui j'ai partagé une discussion professionnelle ou personnelle, derrière un bureau ou une bière: Marc, Alisson, Younes, Mylène, Maxim, Elise, Audrey, Antoine, Florent, José, Apolline, Tatiana, Ramzi, et tant d'autres.

Cette aventure de trois ans est absolument indissociable de la découverte de Chambéry et de sa région, et surtout de l'accueil qui nous y a été fait. Débarqués en 2017 sans connaître personne, nous voilà en 2020 munis d'une bande de copains unie comme les doigts de la main, en dépit de la dure épreuve que nous avons dû affronter cette dernière année. Caro et Clem, un merci pour les soirées coinche arrosées. Adrien, Natan, Margot, Jules, Caro, Alex, Noémie, Pacôme, Solenn, Ju, Laurène, Clément, et tous les autres : merci pour les nocturnes du mardi à la Féclaz, les bières du jeudi soir (ou de n'importe quel autre soir), les weekends chalet en Haute Maurienne, les sorties ski de randonnée au coucher du soleil ... Merci tout simplement de nous avoir adoptés et transformés en vrais savoyards.

Si l'on remonte plus loin, je souhaite aussi remercier les copains de l'INSA. Un merci spécial à mes deux co-docteures, qui ont navigué à travers l'aventure thèse en même temps que moi : à Alice, qui nous avait rendus si fiers en premier il y a un an à Bordeaux, et à Lidia, qui, joli signe du hasard, a brillamment soutenu sa thèse quelques heures avant moi à quelques milliers de kilomètres de là. Merci à toutes les deux pour vos petits messages d'encouragements, vos attentions. Mais aussi merci à tous les autres anciens, pour votre soutien, votre humour, votre amour : Jeanne, Agathe, Armelle, Lucas, Paul, Yoann, Mike, Henri, Josh, où que vous soyez, vous restez les vrais, les essentiels.

Toute mon affection va à ma famille, qui m'a toujours soutenue, poussée, fait grandir. Vous êtes ma fondation, et j'emmène un morceau de vous dans tout ce que j'entreprends. Une petite graine féministe plantée par toi, maman, et arrosée par la suite tous les jours par notre Violette, et que j'essaie de faire pousser autant que possible dans ma vie de tous les jours. Une envie d'aller toujours plus loin, de faire mieux, plus grand, parce mon premier coach personnel, mon papa, a toujours pensé qu'il n'y avait rien que je ne pouvais accomplir. Et bien sûr, un soupçon de combat social, subtilement insufflé par mon indigné préféré, mon Jules. J'ai une pensée émue pour nos grands-parents, Zouzou l'institutrice, Jojo le bricoleur, Grand-Père l'ingénieur, qui auraient je crois été très fiers.

Enfin, merci à mon pilier, ma force tranquille, mon phare contre lequel s'écrasent mes régulières vagues de stress et de panique, Paul. Merci d'avoir accepté de me suivre jusque dans ces montagnes il y a trois ans. Merci d'avoir relu articles et chapitres, avec un regard critique, posé, pertinent, admiratif. Merci de n'avoir jamais douté une seule seconde que cette aventure serait une réussite, merci de croire en moi.

# Table of contents

| ABSTR | RACT                                                                            | I   |

|-------|---------------------------------------------------------------------------------|-----|

| Résun | ИÉ                                                                              |     |

|       | ATION                                                                           | III |

|       | OWLEDGMENTS                                                                     | IV  |

| Table | OF CONTENTS                                                                     | VI  |

| Genei | RAL INTRODUCTION                                                                | 1   |

| 1.    | Solar energy from crystalline silicon                                           |     |

| 2.    | Technological challenges of the silicon sawing process                          |     |

| 3.    | Objectives and outline                                                          | 4   |

| CHAF  | PTER 1 - Mechanical investigations on solar silicon wafers: a literature review | 5   |

| 1.    | Basic knowledge on crystalline silicon                                          | 7   |

| 2.    | Characterizing silicon wafer strength                                           | 11  |

| 3.    | Influence of the crystallization process                                        | 16  |

| 4.    | Influence of the sawing process                                                 | 20  |

| 5.    | Summary and open questions                                                      | 29  |

| CHAF  | PTER 2 - Development of a methodology for thin wafer characterization           | 30  |

| 1.    | Introduction                                                                    |     |

| 2.    | Morphological and structural characterization of wafers                         |     |

| 3.    | Mechanical strength characterization                                            |     |

| 4.    | Investigation of wafer behavior during impact loading                           | 62  |

| 5.    | Discussion                                                                      | 69  |

| 6.    | Conclusion                                                                      | 74  |

| CHAF  | PTER 3 - IDENTIFYING THE CRITICAL DEFECTS RESPONSIBLE FOR WAFER FAILURE         | 76  |

| 1.    | Introduction and approach                                                       | 78  |

| 2.    | Healing wafer surface topography                                                | 81  |

| 3.    | Isolating wafer edge defects                                                    | 103 |

| 4.    | Isolating bulk and subsurface defects by thermal treatment                      |     |

| 5.    | Annealing of as-cut and chemically etched wafers                                |     |

| 6.    | Conclusion                                                                      | 129 |

| CHAF  | PTER 4 - Investigating the key parameters controlling wafer strength            | 131 |

| 1.    | Introduction                                                                    | 133 |

| 2.    | Influence of silicon crystallinity and wafer thickness                          |     |

| 3.    | Influence of the diamond wire sawing process                                    |     |

| 4.    | Conclusion and outlook                                                          |     |

| Genera  | AL CONCLUSIONS AND PROSPECTS                                                         | 185   |

|---------|--------------------------------------------------------------------------------------|-------|

| 1.      | Conclusions                                                                          | 185   |

| 2.      | Perspectives                                                                         | 187   |

| 3.      | Epilogue                                                                             | 190   |

| APPEN   | IDIX A - WEIBULL STRENGTH SIZE EFFECT ON DIAMOND WIRE SAWN SILICON WAFERS            | 191   |

| 1.      | Introduction                                                                         | 191   |

| 2.      | Applying weibull size effect theory to silicon wafers                                | 191   |

| 3.      | Experimental approach                                                                | 194   |

| 4.      | Results                                                                              | 195   |

| 5.      | Conclusions and perspectives                                                         | 196   |

| APPEN   | IDIX B - INFLUENCE OF NUMBER OF TESTED SAMPLES ON ESTIMATION OF WEIBULL PARAMETERS   | 197   |

| 1.      | Introduction                                                                         | 197   |

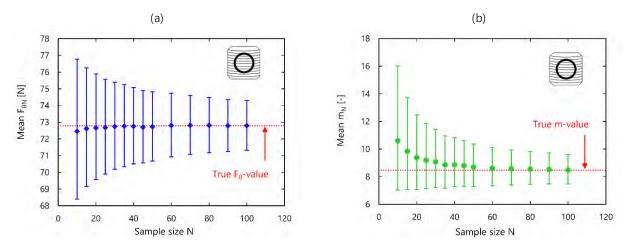

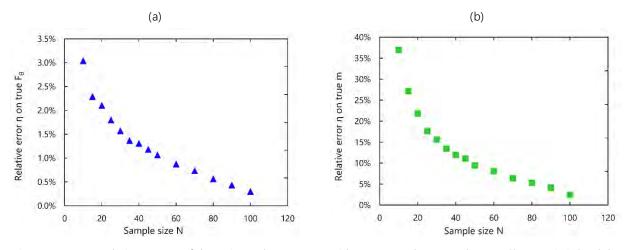

| 2.      | Methodology                                                                          | 198   |

| 3.      | Results for the 4-line bending setup                                                 | 199   |

| 4.      | Results for the RoR setup                                                            | 201   |

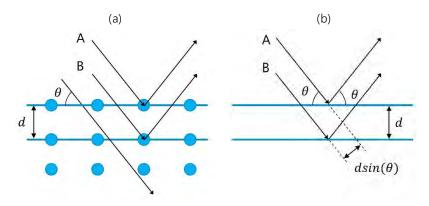

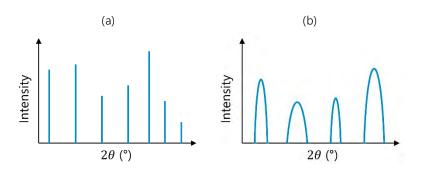

| APPEN   | IDIX C - X-ray diffraction technique to measure residual stresses                    | . 203 |

| APPEN   | IDIX D - Influence of annealing atmosphere on the strength of as-cut wafers          | . 206 |

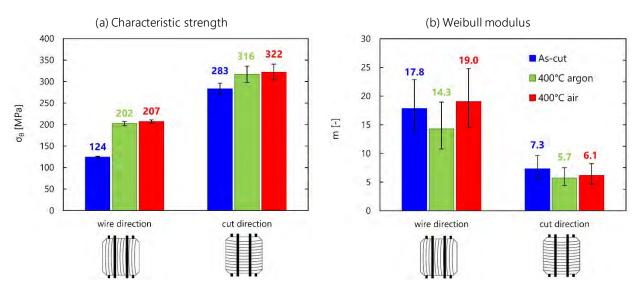

| 1.      | Experimental procedure                                                               | 206   |

| 2.      | Strength results                                                                     | 207   |

| APPEN   | IDIX E - Strength results of all mono-Si wafers tested with the 4-line bending setup | . 208 |

| 1.      | Recall of sawing parameters and designation                                          | 208   |

| 2.      | Results                                                                              | 209   |

| Referei | NCE S                                                                                | 213   |

# General introduction

# 1. SOLAR ENERGY FROM CRYSTALLINE SILICON

#### Solar energy, growing and expanding

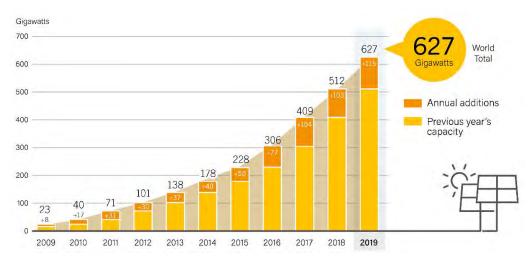

Solar photovoltaic (PV) energy is becoming one of the most competitive options for electricity generation, both for residential and commercial applications. It possesses the highest learning rate of all renewable power technologies - for every doubling of PV shipment volume, module price decreases by 24 % [1] - and is as such now cheaper than fossil fuels in an increasing number of countries [2,3]. In this context, we witnessed a tremendous increase of the worldwide installed PV capacity over the past decade, reaching 627 GW in 2019 - a value to compare to the 23 GW from 2009 (Figure 1).

Figure 1. Evolution of worldwide solar capacity and annual additions [4]

#### Silicon as the key material

A solar cell can be manufactured according to multiple technologies and involving different semiconductor materials. To this day, crystalline silicon remains however the most widely used material: more than 95 % of the PV cells produced worldwide in 2019 use thin silicon slices – **wafers** - as base substrate [5]. This market domination has numerous causes: silicon is the second most earth-abundant element and possesses excellent electrical properties, the corresponding manufacturing techniques are well-mastered, and the cost-to-efficiency ratio of the silicon solar cell is very favourable when compared to other materials.

#### From raw polysilicon to PV module

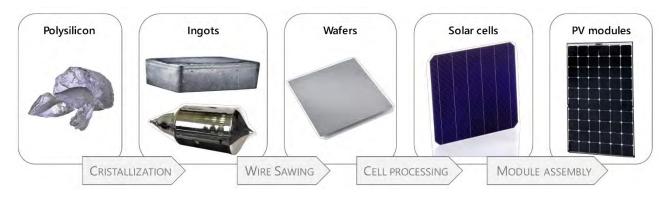

The polysilicon material for the PV chain is obtained by purifying metallurgical grade silicon to a 99.9999 % (six nines or 6N) purity [6]. This so-called solar grade silicon is then melted and solidified into ingots (Figure 2). Depending on the desired cost and material quality, different crystallization techniques can be implemented. For the PV industry, the two main techniques are directional solidification systems (DSS), which allows to obtain multicrystalline silicon, and the Czochralski (Cz) method which yields monocrystalline silicon. After the crystallization process, the ingots are cut into bricks whose lateral dimensions determine the size of the wafers. Each brick is then sliced at once into several hundreds of wafers with a wire saw. The resulting wafers then undergo several processing steps to become solar cells. Chemical processes allow to clean the

wafer and to generate a textured surface that minimizes light reflection. Doping diffusion steps create the electrical junction required to allow the photo current to flow in one single direction. In addition to surface texturing, anti-reflective coating is applied on the surface to further increase the amount of light absorbed. Finally, metal contacts are printed on the wafer to collect the charges carrying the electrical current produced. Several cell architectures exist, which are characterized by their efficiency conversion ratio. The record lab efficiency in 2019 is 26.7 % and 23.2 % for monocrystalline and multicrystalline silicon respectively [7]. The final solar cells are connected in series to increase the tension, and the obtained series are connected in parallel to increase the current. The obtained cell assembly after encapsulation results in a PV module, with average area efficiency (module power / module area) reaching 210 W/m<sup>2</sup> [5].

Figure 2. Manufacturing process of a silicon-based PV module

# Accelerating PV growth

Despite the important achievements in efficiency improvements and cost reduction, the share of solar energy remains marginal (2.8 % of global electricity production [4] in 2019) and above all too low to meet the climate change targets defined by the Intergovernmental Panel on Climate Change (IPCC) through PV deployment. Needleman *et al.* estimated in 2016 that to ensure a higher probability of limiting global temperature rise below 1.5-2 °C, a cumulative PV installed capacity of 7-10 TW by 2030 would be required [8] – in other words, more than ten times the capacity installed in 2019. As pointed out by numerous studies [9–11], such a growth trajectory can only be sustained with drastic reductions of costs and capital expenditure (capex). The latest International Technology Roadmap for PV (ITRPV [5]) emphasizes three strategies to address this challenge:

- Improve module area efficiency

- Introduce specialized module products for different market applications

- Continue cost optimization per piece, by using silicon material more efficiently

This work focuses on the third strategy - in others words, the need to enhance silicon material yield at every stage of the PV manufacturing chain. As discussed in the following section, a very large share of this yield is attributable to the sawing step.

# 2. TECHNOLOGICAL CHALLENGES OF THE SILICON SAWING PROCESS

### A crucial step for material and cost savings

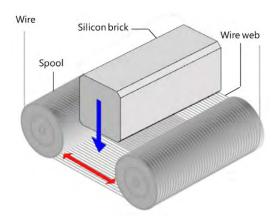

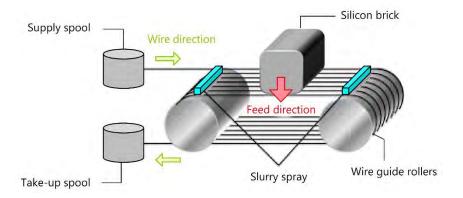

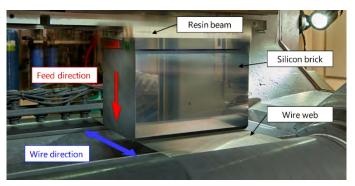

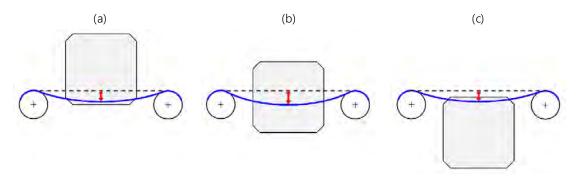

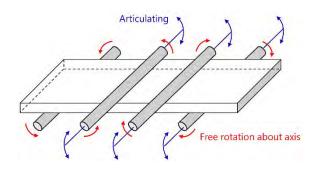

Although some alternative processes are under study [12,13], more than 95 % of silicon wafers for PV applications are obtained by wire sawing. The basic working principle is illustrated in Figure 3: the cutting wire, which moves at a few tens of meters per second, is wound multiple times around two cylinders to form a web. The silicon brick is moved down through this moving web, allowing several hundreds of wafers to be generated in once. This manufacturing step is of significant economic importance, as it still accounts for 15 %

of the final PV module cost [5]. More specifically, the major inherent drawback of the wire sawing process is the material waste: for each wafer obtained, a thin layer of material corresponding to the cutting line, called the *kerf*, is lost. Therefore, with a standard wafer thickness of 170  $\mu$ m for a kerf width of 75  $\mu$ m in 2019 [5], about 30 % of the material available in a brick gets lost in the form of a silicon powder. While promising recycling applications for this kerf are being developed [14], optimizing material yield during the sawing step remains a crucial objective. In practice, this implies reducing both wafer as-cut thickness (i.e., thickness right after the sawing step) and kerf width.

Figure 3. Schematic layout of the wire sawing process

### Towards thinner wafers

Decreasing as-cut thickness is indeed a way to generate more wafers per silicon brick. As a demonstration, Liu *et al.* [11] calculated that decreasing wafer thickness from 160 to 50  $\mu$ m can potentially get a capex reduction of ~ 0.14 \$/(W/year) and a cost reduction of ~ 0.07 \$/W of the current PV module <sup>1</sup>, which in 2019 had an average price of 0.26 \$/W [5]. Even though decreasing wafer thickness can deteriorate the final solar cell efficiency due to an incomplete absorption of photons, recent studies all estimate the threshold value to be between 50  $\mu$ m and 100  $\mu$ m depending on the cell architecture [11,15,16] – i.e., well below the industry standards. There is therefore still much room for improvement regarding wafer thickness.

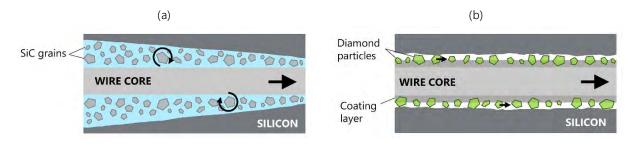

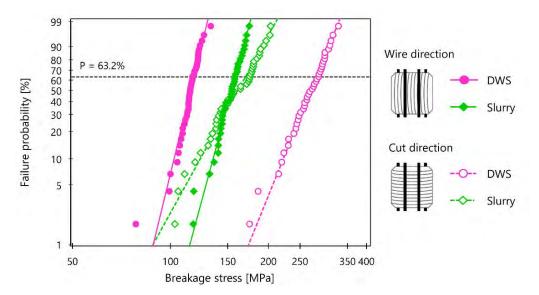

#### Diamond wire sawing as dominant technology

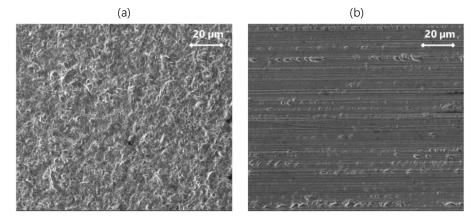

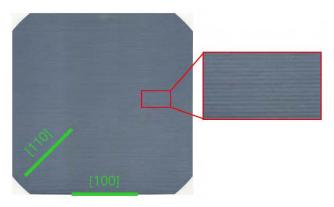

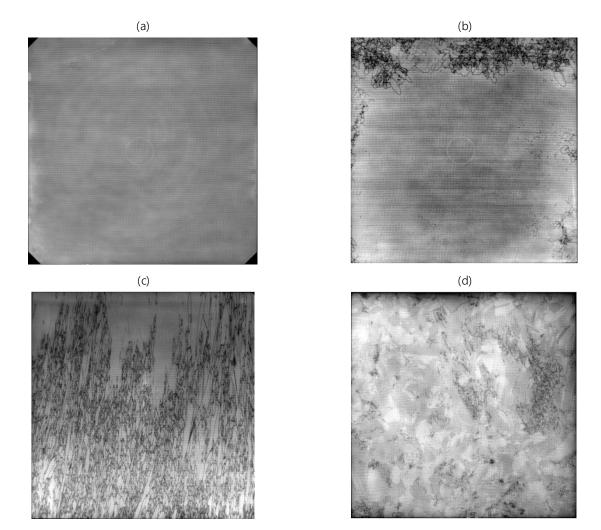

In the context of a need for kerf reduction and increased productivity, we witnessed an abrupt change in the past ten years, with diamond wire sawing (DWS) technology completely replacing the historical loose abrasive slurry (LAS) sawing technique. The market share of DWS officially reached 100 % in 2018, while in 2016 it was only 45 % and 5 % for monocrystalline and multicrystalline silicon, respectively [5,17]. Thinner wire core, lower cutting time and lower capex are among the unquestionable advantages of DWS that justified this extremely fast shift in technology [18,19]. However, the mechanical damage generated by this new abrasion process has proven to be complex, anisotropic and above all fundamentally different from that of the LAS technique [20,21]. Ever since the appearance of DWS, characterizing this damage has been the subject of extensive work [22–24], but its exact nature and influencing parameters are to this day not entirely known or understood.

<sup>&</sup>lt;sup>1</sup> In comparison, they show that increasing cell efficiency from 19 % to 24 % by implementing advanced technologies only decreases capex by ~ 0.08 \$/(W/year) and cost by ~ 0.07 \$/W.

#### What about the wafer breakage rates?

Common to both the as-cut thickness reduction and the extremely fast development of DWS is their potential influence on the mechanical behaviour and properties of the resulting wafers. On the one hand, several studies measured indeed higher breakage rates when processing thinner wafers [25]. On the other hand, it has been repeatedly demonstrated that as-cut DWS samples exhibit anisotropic mechanical properties, with a critically lower measured fracture strength depending on the orientation of the applied load [26–28]. This dual influence is precisely where the scientific and economic challenge lies: lower thickness and DWS technology were both introduced as a pathway towards a better use of silicon material. However, if they induce higher breakage rates of the wafers during solar cell processing, we may question their actual benefits.

Therefore, enhancing silicon material yield during the sawing process will lead to cost savings only if the resulting wafers exhibit reliable and controlled mechanical strength.

# **3. O**BJECTIVES AND OUTLINE

In this work, we aim to improve our understanding of the mechanical properties of silicon wafers and to identify the most influencing mechanisms. We concentrate on the behaviour of as-cut samples, i.e. which were collected directly after sawing, because all subsequent solar cell processing steps (chemical cleaning, texturing, etc.) will help enhance their fracture strength. In other words, the time when a wafer is the more likely to break is following the sawing process, which is where our focus lies. The main ambition of our study is to be able to establish recommendations for the manufacturing parameters of thin silicon wafers – from crystallization to sawing - as well as to propose adjustments of the handling and processing technologies to limit breakage rates. The present work is based on mechanical fracture tests performed on more than seven thousands of samples, in combination with finite element modelling methods. In our methodology, we particularly benefited from using wafers that were cut in our lab using controlled parameters. The manuscript develops in four main chapters:

- Chapter 1 provides a state of the art overview of the mechanical investigations performed on PV silicon wafers. We present the theoretical properties related to the crystallographic structure of silicon, as well as the existing experimental characterization methods. The two main processing steps of silicon wafer manufacturing - crystallization and sawing - and their known influence on sample strength are discussed in detail. This literature review allows us to highlight the yet unanswered questions that guided our work.

- In Chapter 2, we develop the different methods implemented to characterize a typical as-cut wafer as comprehensively as possible. We introduce the non-destructive techniques chosen to analyse the structural and morphological defects of the samples, as well as the destructive fracture tests. This thorough methodology allows us to define characterization guidelines for the rest of our work.

- Chapter 3 aims at determining which of the defects present in a typical as-cut DWS wafer are the most critical for mechanical failure. To this end, we propose an original systematic procedure to isolate their respective influence on the fracture properties of the samples.

- In Chapter 4, we conduct an extensive mechanical characterization of silicon wafers from different crystalline nature, different as-cut thicknesses and sawn using different slicing parameters. Our goal is to determine whether we can find a combination of crystallization and sawing parameters to obtain the most mechanically reliable thin wafer.

- 4 -

• We finally draw the General conclusions of our work and propose some prospects.

# CHAPTER I Mechanical investigations on solar silicon wafers: a literature review

Studying the mechanical properties of silicon wafers has always been a subject of interest for the PV research and industry, as they often dictate the fundamental limits on the handling and processing steps of the future solar cells. This chapter aims at giving a state of the art overview of mechanical investigations on solar silicon wafers. The first part deals with basic crystallographic knowledge of silicon and the resulting elastic and fracture properties of the crystal. The second part introduces the experimental and statistical approaches to characterize silicon fracture strength and behavior. The third and fourth parts present the two main processing steps needed to manufacture a typical solar wafer: crystallization of silicon raw material into a solid ingot and wire sawing of the brick. The defects associated with each process and their influence on the mechanical properties of the resulting wafers are discussed. We finally put forward some open questions.

# Contents

| 1. BAS | SIC KNOWLEDGE ON CRYSTALLINE SILICON                                 | 7  |

|--------|----------------------------------------------------------------------|----|

| 1.1.   | Elastic properties                                                   | 8  |

| 1.2.   | Fracture properties                                                  | 9  |

| 2. Сн  | ARACTERIZING SILICON WAFER STRENGTH                                  | 11 |

| 2.1.   | Destructive mechanical testing                                       | 11 |

| 2.2.   | Statistical description of brittle fracture: Weibull theory          | 13 |

| 3. Inf | LUENCE OF THE CRYSTALLIZATION PROCESS                                |    |

| 3.1.   | Silicon crystallization techniques                                   | 16 |

| 3.1.   | 1. Czochralski process                                               | 16 |

| 3.1.   | 2. Directional solidification process                                | 17 |

| 3.2.   | Link between crystallization defects and wafer mechanical properties |    |

| 4. INF | LUENCE OF THE SAWING PROCESS                                         |    |

| 4.1.   | Wire sawing cutting processes                                        |    |

| 4.2.   | Damage and defects generated during sawing                           | 22 |

| 4.2.   | 1. Origin of defects: brittle and ductile mode machining             | 23 |

| 4.2.   | 2. Damage layer concept                                              | 25 |

| 4.3.   | Link between sawing induced damage and wafer mechanical properties   |    |

| 5. Sui | MMARY AND OPEN QUESTIONS                                             |    |

# 1. BASIC KNOWLEDGE ON CRYSTALLINE SILICON

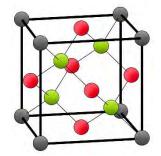

Crystalline silicon owns a diamond crystalline structure, which can be described as a pair of intersecting facecentered cubic lattices, each of them being separated by one fourth of the width of the unit cell in each dimension. Each atom connects with four neighbor atoms via covalent bonds. A unit cell is composed, as shown in Figure 1.1, of eight atoms at the corners (in grey), six atoms at the center of faces (in red) and four extra atoms resting inside the lattice (in green) at the centroid of 4 tetrahedrons [29].

Figure 1.1. Face-centered cubic crystal structure of silicon

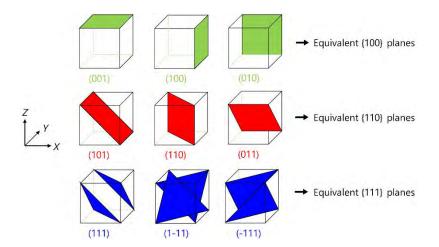

The crystal planes and crystallographic directions are commonly defined by the Miller indices h, k and l as indicated Table 1.1 [30]. The cubic symmetry of the structure implies that there are 24 equivalent possibilities to position the single crystal in a Cartesian coordinate system [31]. This means that a single direction (or plane<sup>2</sup>) associated with h, k and l for any sign of each and in any order belongs to the same direction (or plane) family defined by positive h, k and l. Figure 1.2 shows the {100}, {110} and {111} family of planes, which are the most studied ones in silicon. The crystal planes in each family are identical.

| Notation    | Interpretation                 |

|-------------|--------------------------------|

| (hkl)       | Single crystal plane           |

| $\{hkl\}$   | Equivalent planes (family)     |

| <hkl></hkl> | Single crystal direction       |

| [hkl]       | Equivalent directions (family) |

Since the atom density differs from one crystallographic direction to another, the physical properties of single crystal silicon exhibit anisotropic characteristics, such as thermal expansion coefficients, surface energies, and electrical resistivity. In particular, this anisotropy dominates the elastic and fracture behavior of silicon.

Crystalline silicon can exist in its monocrystalline form as a single, continuous and unbroken crystal, or in multicrystalline form. In this case, the material consists of multiple small silicon crystals (grains) separated by grain boundaries. In the solid state, silicon can also exhibit a non-crystalline amorphous form, in which the long-range order of the tetrahedral structure is not present anymore: atoms form a continuous random network and some of them exhibit dangling bonds<sup>3</sup>, which can cause degradation of the electrical properties.

<sup>&</sup>lt;sup>2</sup> According to the Miller indices, a crystallographic plane is defined with its normal direction.

<sup>&</sup>lt;sup>3</sup> In chemistry, a dangling bond is an unsatisfied valence on an immobilized atom.

Figure 1.2. Crystallographic planes in single cystal silicon

#### 1.1. Elastic properties

The anisotropic elastic behavior of single-crystal silicon can be described by the fourth-order stiffness tensor C owning three independent parameters  $C_{11}$ ,  $C_{12}$  and  $C_{44}$  in the crystallographic coordinate system of principal axes [100], [010] and [001]. At room temperature and ambient pressure, the measurements considered as the most accurate in the literature were reported by Hall [32] with acoustic wave propagation in the solid and are recalled below:

The orthotropic nature of this tensor allows to determine the usual elasticity constants of a material, such as the Young's modulus E, Poisson's ratio v and shear modulus G in any direction of interest [33]. In particular, the Young's modulus of monocrystalline silicon is minimal (130 GPa) in the [100] direction and maximal (188 GPa) in the [111] direction. It is important to understand that the stiffness tensor from equation (1.1) is valid for a monocrystalline silicon sample owning the default *XYZ*-axes, i.e. *X* is <100>, *Y* is <010> and *Z* is <001>, as shown in Figure 1.2. In order to obtain the elasticity constants in any arbitrary direction, the stiffness tensor *C* must be rotated so that one of the axes is aligned with the direction of interest [34]. The expression for the rotated *C'* can be found in literature [35,36] and is more easily calculated using algebraic notations:

$$C'_{ijkl} = \sum_{p=1}^{3} \sum_{q=1}^{3} \sum_{r=1}^{3} \sum_{s=1}^{3} Q_{pi} Q_{qj} Q_{rk} Q_{sl} C_{pqrs}$$

(1.2)

where Q is the rotation matrix. This tensor rotation requires tedious calculations that can however easily be performed numerically with a computer program.

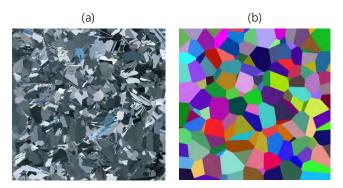

As an aggregate of multiple single crystals separated by grain boundaries, multicrystalline silicon theoretically owns an intermediate value of Young's modulus between 130 GPa and 188 GPa. If the aggregate contains a sufficiently large number of grains and is macroscopically homogeneous [37], the sample can be seen as an elastically isotropic material described by two parameters, the Young's modulus and the Poisson's ratio. This so-called aggregate theory has been widely applied to microelectromechanical systems (MEMS) [38], which have grains of nanometric or micrometric size. However, depending on the growth process parameters, the grain size of a PV silicon multicrystalline wafer can vary between some hundreds of micrometers to a few

centimeters. In the latter case, the grain size is almost the same order of magnitude as the sample dimensions, as illustrated in Figure 1.3.a. Funke *et al.* [39] performed an analytical calculation considering a uniform orientation distribution of the grains in a representative volume element and obtained E = 162.5 GPa and v = 0.223. Zhao *et al.* [40] proposed a different approach based on a numerical model, in which the grain structure of the wafer is generated by a Voronoi tessellation <sup>4</sup> as illustrated in Figure 1.3.b. The resulting wafer is thereafter introduced in a finite element (FE) model reproducing a 4-line bending test, and the equivalent Young's modulus, calculated from the slope of the load-deflection curve, is assessed as  $163 \pm 2$  GPa. The negligible difference in value between the two methods seems to validate the homogenization hypothesis made by Funke *et al.*

Figure 1.3. Example of a (a) PV multicrystalline silicon wafer and (b) Voronoi tesselation

### 1.2. Fracture properties

At room temperature, silicon is a purely brittle material: when solicited, it deforms elastically until fracture, with no movement of dislocations and therefore no plastic deformation. If considered as a perfect single-crystal with no structural defects, silicon actually owns a very high intrinsic strength: *ab initio* theory allowed to calculate the ideal tensile strength of silicon to be 22 GPa [41], while notch-free fracture experiments performed on high-quality mirror polished monocrystalline silicon samples provided tensile strength values between 3-7 GPa [42].

However, as soon as a microscopic defect exists in the wafer, the fracture strength is significantly reduced and even a moderate stress value may initiate failure. The linear elastic fracture mechanics (LEFM) theory explains this phenomenon by a dramatic increase of the local stress in the region of the defect. LEFM theory shows that, regardless of the loading and the sample geometry, the solution of the stresses in polar coordinates (r,  $\theta$ ) with the origin at the crack tip is:

$$\sigma(r,\theta) = \frac{K_{\alpha}}{\sqrt{2\pi r}} \cdot f_{\alpha}(\theta)$$

(1.3)

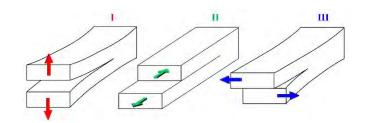

where  $\alpha = I$ , *II* or *III* are known as the cracking modes used to classify the fracture problems depending on the loads applied to the crack (Figure 1.4).  $K_{\alpha}$  is the stress intensity factor that depends on the sample and crack geometry and  $f_{\alpha}$  is a dimensionless function of the coordinate angle  $\theta$ . For example, in the case of a straight crack of length 2a subjected to a uniform tensile stress  $\sigma$ , the concentration factor  $K_I$  is expressed as:

$$K_I = \sigma \cdot \sqrt{\pi a} \tag{1.4}$$

<sup>&</sup>lt;sup>4</sup> A Voronoi diagram (or tessellation) is a partition of a plane into regions close to each of a given set of objects.

Figure 1.4. Elementary fracture modes. Mode I: opening - Mode II: in-plane shear - Mode III: out-of-plane shear

The resistance of the material against crack growth determines whether an existing crack remains stationary or starts to propagate. LEFM states that crack growth initiates as soon as the stress intensity factor reaches a critical value  $K_{IC}$ , called the fracture toughness. In the same way as for the elastic properties, fracture toughness of single crystalline silicon depends on the crystallographic orientation [33]. This anisotropic toughness is commonly measured by Knoop or Vickers micro-hardness indentation sometimes associated with bending tests [43,44] or with double-cantilever beam tests [45,46]. Toughness can also be calculated by molecular dynamics [47] or density functional theory [48]. The values reported in literature are either expressed in terms of fracture toughness  $K_{IC}$  or surface energy <sup>5</sup>, and may vary strongly depending on the testing method, specimen surface preparation and crack length. It is however agreed upon that silicon has two principal cleavage planes: the {111} and {110} planes, which exhibit lower toughness than other planes and are therefore preferential fracture paths. Fracture of single crystalline silicon is moreover a dynamic process, with crack propagation velocities reaching up to 3700 m/s [49].

Above a certain temperature, a brittle to ductile transition is observable, a phenomenon which was first revealed in the 1950s [50,51]. Investigations on single crystal silicon were widely conducted via fracture tests on pre-cleaved specimens, in order to capture and model the transition from pure cleavage to general plasticity [52–54]. As temperature increases, transition is dictated by the emission and motion of dislocations near the crack tip, which blunt the crack front and increase the material toughness compared to room temperature [55].

The transition temperature value is a function of the silicon type, the strain rate, the crystallographic orientation and the doping level. It has been measured around 600 °C, which is much higher than most of the operating temperatures of silicon-based systems – temperature at the surface of a solar module rarely exceeds 100 °C. In service, silicon remains therefore brittle and plasticity is far from nucleation. However, depending on the solar cell architecture, a silicon wafer may undergo a certain number of high temperature steps, such as the diffusion of the dopant material-containing coating, which takes place at temperatures around 850 [56], or the deposition of the metallic contacts on the wafer, which involves a peak firing temperature of up to 1000 °C [57]. If initial microcracks are present in the wafer during these high temperature steps, crack plasticity may occur, although its effect on the mechanical properties of the solar cells is rarely considered [58].

<sup>&</sup>lt;sup>5</sup> The toughness  $K_{IC}$  equals twice the surface energy of the fracture plane  $\gamma$  in the case of quasi-static crack propagation in a brittle material, and becomes larger than  $2\gamma$  when plastic deformation occurs at the crack tip.

# 2. CHARACTERIZING SILICON WAFER STRENGTH

### 2.1. Destructive mechanical testing

Silicon wafers for PV applications are square or pseudo-square thin plates with an extremely high length-to-thickness ratio: they have a typical size of  $156 \times 156 \text{ mm}^2$  with thickness ranging from 100 to 180 µm. The length-to-thickness ratio is moreover expected to become more important, as wafer format is quickly shifting towards higher lateral dimensions ( $166 \times 166 \text{ mm}^2$  wafers are already in production, while  $210 \times 210 \text{ mm}^2$  are being introduced in the market) and lower thicknesses (for certain cell architectures, 160 µm is already mainstream [5]). It is worth noting that up to recently, no standard test method existed to evaluate the mechanical strength of silicon wafers. The test setup and sample geometry are therefore chosen based on existing literature as well as on practical criteria – it is for instance very difficult to perform tensile tests on thin brittle specimens such as silicon wafers.

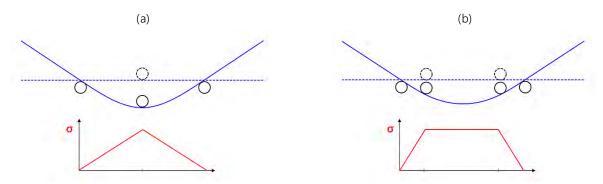

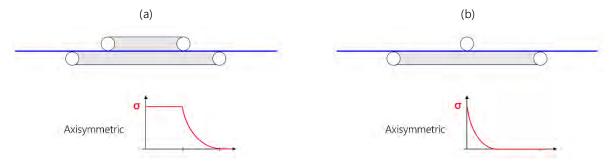

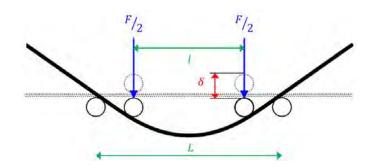

At the wafer scale, the most widely used methods are uniaxial bending setups, in which the loading devices are in the form of cylindrical bars, thus creating a linear contact with the sample surface. The 4-line bending configuration is usually preferred over 3-line bending, as it enables to have a large area of the tested sample submitted to a uniform mechanical state [31] (Figure 1.5). Silicon is indeed a crack-sensitive material and fracture mechanics predicts that the failure will initiate on the tensile lower surface of the sample, where the largest crack is located. Imposing a uniform tensile load on a significant sample area thus improves the representativeness of the test procedure in terms of wafer defect population [59].

Figure 1.5. Schematic setup and theoretical maximum tensile stress distribution in (a) 3-line (b) 4-line bending test

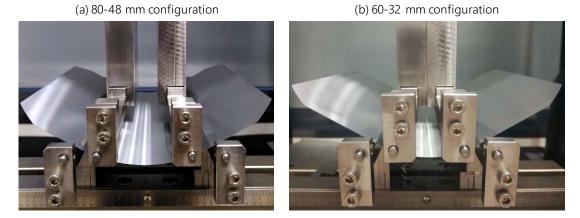

Based on the similarities in brittle fracture behavior, several studies choose to design their 4-line bending setup according to the guideline of ASTM standards for technical ceramics [40,60,61]. However, their recommendations are often not suited to the high length-to-thickness ratio of PV silicon wafers. In order to overcome this issue, a standard test method for strength testing of PV wafers was recently developed, which provides requirements to design a 4-line bending setup suited for full-size silicon wafers and lookup tables to compute fracture stresses [62]. However, given the recentness of this contribution, there are yet only very few studies relying on it [27]. The uniform stress distribution over the whole wafer area implies that different types of defects are loaded, mainly surface and edge defects, and to a lesser extent volume defects. The 4-line bending method therefore has the advantage of being more sensitive to the overall wafer damage, but may be limiting if there is a need to focus on a specific defect population.

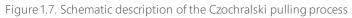

This is the reason why some studies implement biaxial bending methods, mostly in the form of Ring on Ring (RoR) [63–65] or Ball on Ring (BoR) setups [66]. In these configurations, the wafer is supported by an annular support and loaded either by a ring of smaller diameter for the RoR setup or by a sphere for the BoR configuration. The main advantage of this test geometry is that the stress is theoretically zero at the

wafer edges and maximum at the center of the sample, and in particular in the case of the RoR setup, uniform over the whole area below the loading ring (Figure 1.6). This method thus allows to eliminate the influence of defects located at the edges of the wafer and to concentrate on the study of surface or volume defects.

Figure 1.6. Schematic setup and theoretical maximal tensile stress distribution (a) RoR and (b) BoR test

However, the analytical formula for the stress distribution as depicted in Figure 1.6, introduced by Vitman and Pukh [67], is only valid under strict and restrictive conditions. In particular, the maximum wafer deflection should not exceed half the thickness. In order to meet these requirements, the setup can be designed based on the ASTM standard for equibiaxial flexural strength of advanced ceramics [68], as done in several studies [64,65]. Complying with this standard requires, however, to work with extremely small samples (in the order of 1 × 1 cm<sup>2</sup>) and therefore to evaluate a very restricted area of the wafer (4 % of the surface). This not only reduces the representativeness of the results, but it also calls for an extra dicing step that could, very much itself, modify the results. Some studies alternatively choose to design a RoR setup with dimensions suitable to test an entire wafer [63], thus requiring specific care when analyzing the stress results as the analytical formulae are no longer valid.

A few limited works combine the previous bending methods with twist tests [69,70], but the highly inhomogeneous stress field generated in the wafer makes the interpretation of the results difficult and explains the little interest raised by this technique.

The aforementioned tests are quasi-static methods, i.e. the force or displacement is applied at a sufficiently low speed (usually adjusted to have a strain rate between 10<sup>-5</sup> and 10<sup>-1</sup> s<sup>-1</sup> on universal testing machines) so that inertia effects can be neglected. While these methods are of high practical interest, they are not entirely representative of the "real" stresses experienced by a wafer during handling and transporting. A more suited alternative is to apply dynamic loads to the wafer in the form of impact tests. Such methods are however rarely implemented, mainly because the required energy levels are very low (in the order of a few mJ) and therefore difficult to control. Notable exceptions either involve a setup with a wafer falling on a collision body [71,72] or a pendulum-like system allowing to introduce a controlled amount of impact energy on the wafer edge [73]. Strength evaluation of silicon wafers can even be taken a step further by designing specific setups that reproduce as closely as possible the actual handling conditions (wafer singulation and placement in carriers, gripping, carrying, and turning actions) [74]. The main advantage is that the results could be directly transformed into design recommendations for industrial equipment or processes. Conceiving such systems is however complex and costly and the number of applications remains very limited.

Within a more local approach, indentation tests are also often employed to characterize the facture behavior of silicon wafers. These methods can indeed be used to measure local mechanical properties such as hardness or toughness [44,75], but also to create artificial cracks in silicon wafers, with the aim to mimic the damage existing in a PV wafer [76]. Inserting these artificial defects can help comprehend the mechanisms

of crack propagation, for example by determining which cracks will more likely propagate and lead to failure under a given loading configuration [77], or how different cracks can interact with one another [78].

It should be mentioned that there has been evidence of fatigue behavior in micro- or nanoscale silicon samples [79,80] and the topic has recently gained some interest for MEMS applications [81,82]. While several hypotheses were proposed to explain this fatigue behavior, none of the mentioned mechanisms were ever observed at the PV silicon wafer scale. Moreover, the level of stresses at stake in the existing experimental studies, in the order of a few GPa, is about two to three orders of magnitude higher that the strength values usually measured in PV silicon wafers. This explains why in the PV industry, subcritical crack growth (fatigue) problem is not taken into account when evaluating the mechanical reliability of silicon wafers.

The study of mechanical integrity in the PV field also recently extended to the solar cell and module scale. Blakers and Armour [83] showed that under repeated non-destructive bending, solar cells either broke on the first flexure or did not break at all. Mechanical studies on solar cells and modules usually focus on the formation of microcracks during mechanical loading and their impact on module performance. Kajari-Schröder *et al.* provided a statistical analysis of the spatial distribution of cracks with the electroluminescence method [84]. Sander *et al.* studied crack patterns in solar cells based on 4-line bending tests and highlighted that the cell strength varies with the orientation of the busbars [85]. Kaule *et al.* obtained the same result and coupled their experimental values with a FE model taking into account all the components of the solar cell [86]. More recent studies showed that at the module scale, cell cracking was also related to a fatigue degradation phenomenon during cycling bending, which is caused by the encapsulation of the cells in a polymer generating residual thermo-elastic stresses [87]. Borri *et al.* showed moreover that this fatigue crack growth originates from the soldering point between the busbar and the solar cell [88].

# 2.2. Statistical description of brittle fracture: Weibull theory

# Some elements of the literature review described in the following paragraph were quoted verbatim from an article published by Carton et al. [89].

Breakage stress values obtained for silicon wafers that are deemed identical will exhibit large scattering. This dispersion results from the brittle nature of silicon: the strength of a silicon wafer is ultimately controlled by the density, size and geometry of its defects, which can vary strongly even within a series of samples from the same ingot. These characteristics are random variables, and the failure stress of the wafer under a given applied load becomes a statistical data. Failure is then a random event with a certain probability or likelihood of coming true under given circumstances. The mean stress value is therefore not sufficient to represent the strength of a set of wafers and the data require statistical treatment.

There exist different statistical approaches to model brittle failure, which all aim at linking the characteristics of the defect population and the characteristics of the stress field to the material failure probability. Because of its ability to evaluate both the level and the scattering of strength values, Weibull probability function [90] is the most widely used one to describe the fracture behavior of silicon wafers. In the specific case of wafers for PV applications, Weibull is, to the best of our knowledge, the only implemented model. The fundamental assumption for Weibull's statistical theory of fracture [91] is the weakest link hypothesis: the survival probability of a specimen is the product of survival probabilities of each volume element within the specimen [92]. The mechanical strength of the entire specimen is therefore defined by its weakest defect. For a uniaxial homogeneous tensile stress state, Weibull theory assumes that each volume element possesses the same probability of failure and the general 3-parameter distribution gives the probability *P* for a specimen of volume *V* to fail when subjected to a uniaxial tensile stress  $\sigma$ :

$$P(\sigma, V) = 1 - \exp\left(-\frac{V}{V_0} \left(\frac{\sigma - \sigma_u}{\sigma_0}\right)^m\right)$$

(1.5)

where *m* is the Weibull modulus (known as the shape parameter),  $\sigma_0$  is the characteristic strength value (scale parameter), and  $\sigma_u$  the threshold stress below which the specimen will not fail (location parameter). The Weibull modulus describes the scattering of the results (a higher value of *m* means a small variation in strength) while  $\sigma_0$  represents the level of stress at which 63.2 % of the samples will fail. This distribution thus depends on the volume of the loaded sample, a phenomenon known as the "size effect": for a given volume, a sample with more defects is more likely to fail than a sample with less defects. Conversely, a sample of greater volume has a greater chance of having a critical defect than a smaller sample.  $V_0$  is the chosen normalizing volume, which allows to adjust the dimension of the shape parameter. In most cases, for the sake of simplicity, the threshold stress is assumed to be zero, and the distribution can be reduced to a simplified 2-parameter form:

$$P(\sigma, V) = 1 - \exp\left(-\frac{V}{V_0} \left(\frac{\sigma}{\sigma_0}\right)^m\right)$$

(1.6)

This simplification allows to obtain a conservative prediction, and the remaining two parameters are much simpler to estimate [93]. Several studies discussed the effect of assuming  $\sigma_u = 0$  on the estimation of the Weibull parameters [94,95]. Lu *et al.* [94] proposed a quantitative procedure to highlight the effects of the threshold stress and concluded that a compromise should be made between simplicity of the 2-parameter distribution and applicability of the 3-parameter distribution as the threshold stress of the considered samples increases. Malzbender *et al.* [96] demonstrated that for fracture characterization of thin ceramic components, the 3-parameter Weibull distribution is more appropriate. More recently, Deng *et al.* [95] conducted an extensive examination based on Monte Carlo simulations and showed that the 2-parameter Weibull function is sufficiently suitable for the description of the statistical variation of the measured strength sample, regardless of whether the strength follows a 2-parameter of 3-parameter Weibull distribution.

When working with silicon wafers, almost all studies choose to restrict the strength distribution to a 2-parameter function. A first notable exception can be found in the work of Saleh *et al.* [97], who used a 3-parameter function to describe the strength of polycrystalline wafers. However, their investigations were performed on MEMS samples (i.e. for electronic and not PV applications) with extremely high strength values (in the order of 2-5 GPa), thus justifying the use of a threshold stress value, while failure stresses for solar silicon wafers rarely exceed a few hundreds of MPa. There exist, to the best of our knowledge, only two studies applying 3-parameter Weibull distribution to silicon wafers for PV applications: Cereceda *et al.* [98] performed RoR tests on wafers with drilled holes for back contact cell application, while Barredo *et al.* [99] carried out 4-line bending tests on wafers of different silicon crystallinity.

In the case where a non-uniform stress state is applied on the specimen, as it is the case for most of the bending tests <sup>6</sup> chosen for silicon wafers and described above, each volume element has a different failure probability. The formulation of equation (1.6) becomes an integral over the entire specimen volume:

$$P(\sigma, V) = 1 - \exp\left[-\frac{1}{V_0} \int_V \left(\frac{\sigma(x, y, z) - \sigma_u}{\sigma_0}\right)^m dV\right]$$

(1.7)

The three parameters  $(m, \sigma_0, \sigma_u)$  are associated with the material and are independent of size or stress distribution within the sample. However, taking into account the size effect requires a complex iterative

<sup>&</sup>lt;sup>6</sup> In the bending tests described in the previous section, there exists a stress gradient along the thickness of the sample, with a maximal compression stress on the upper surface and a maximum tensile stress on the lower surface.

procedure that involves the calculation of an equivalent volume (or area) submitted to a uniaxial constant load [100], thus ensuring that equation (1.7) is valid. This is the reason why nearly all existing studies choose to neglect this effect, which is justified by the use of a given sample geometry (for example a 156 × 156 mm<sup>2</sup> wafer of thickness 180  $\mu$ m) and identical test dimensions, so that the loaded volume can be considered similar throughout their work. Since the important data is usually the strength comparison between different sets of wafers rather than the actual strength value, the equivalent volume (or area) is considered as unity [98]. This assumption yields a much simpler expression for the probability of failure:

$$P(\sigma, V) = 1 - \exp\left[-\left(\frac{\sigma - \sigma_u}{\sigma_\theta}\right)^m\right]$$

(1.8)

It is however very important to mention here the change in parameter designation for the characteristic strength, from  $\sigma_0$  to  $\sigma_\theta$  : while  $\sigma_0$  is independent of the tested size,  $\sigma_\theta$  depends on the stress distribution and size of the tested sample, i.e. on the type and geometry of setup used. This essentially means that the stress distribution values obtained by neglecting the size effect from different setups (for example, between a RoR and a 4-line bending setup, but also between two 4-line bending setups with different dimensions) are in theory not comparable. This effect had however never been verified experimentally for solar silicon wafers. We conducted a specific experimental study to explore this problem, which compares the Weibull strength parameters obtained from wafers tested with three different bending setups. The results were published in a separate article [89] and are synthesized in **Appendix A**.

Despite its wide applicability, Weibull's theory has been called into question since its first introduction. The main criticism is the macroscopic nature of the approach: it acknowledges the existence of defects within the material but does not take into account their characteristics such as size, orientation or density. A significant amount of research has therefore been made in the last fifty years to implement models with a more physical basis. Batdorf considers the defects as longitudinal cracks and introduces a distribution function which expresses the density of cracks with a strength exceeding a critical defined stress value [101]. Several other models were developed based on this concept of defect density function, which is determined either *a priori* via a mathematical distribution as in Batdorf's model or *a posteriori* by analyzing the defects in the material. For example, Poloniecki proposes an expression for the defect density function with respect to the uniaxial stress direction [103].

These non-exhaustive examples add a physical meaning to Weibull's probabilistic model, by trying to characterize the physical reality of the material microstructure. However, they introduce additional parameters that are difficult to quantify experimentally. For a silicon wafer typically, it would imply creating a distribution function that accurately describes the size, density and orientation of all-existing defects within the material. Yet, as we will understand in the following sections, a silicon wafer possesses of a multitude of defects of different natures, sizes, shapes and densities generated during its manufacturing process, from crystallization to sawing.

# 3. INFLUENCE OF THE CRYSTALLIZATION PROCESS

The crystallization process of a silicon ingot not only determines the structural quality of the material but also the chemical contamination, two parameters that can strongly influence the mechanical properties of the obtained silicon. Crystalline silicon for PV applications exists in three forms:

- monocrystalline silicon, which is grown by the Czochralski process

- multicrystalline silicon, which is grown by directional solidification processes

- quasi-monocrystalline or **mono-like** silicon, which results from a specific application of the directional solidification process

In order to modulate the electrical and optical properties of the material, doping impurities are added to the silicon feedstock during the crystallization step. When the doping element possesses five valence electrons, such as phosphorus (P), the fifth electron is free to move within the crystal when a voltage is applied. The majority charge carriers are electrons and the resulting silicon is an n-type (for negative charge) semiconductor. Conversely, if the doping impurity only has three electrons such as boron (B), it leaves a vacant location called a hole, which can accept an electron. The majority charge carriers are holes and p-type silicon has a positive charge. It should be noted that Gallium (Ga) has been very recently gaining significant interest as replacement of boron for doping of p-type silicon [104].

The different crystallization techniques and associated silicon properties and defects are detailed in the following sections.

# 3.1. Silicon crystallization techniques

### 3.1.1. Czochralski process

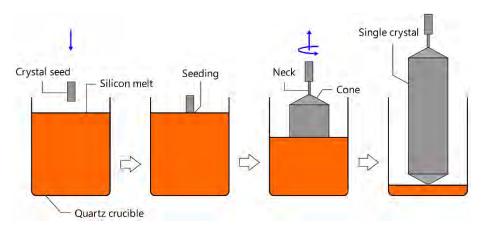

Silicon crystal growth by the Czochralksi (Cz) technique begins with melting electronic grade (9N) polysilicon chunks or grains together with possible doping elements in a high purity quartz crucible. A small crystal seed with a specific crystallographic orientation <sup>7</sup> attached at the end of a cable is dipped into the melt, and slowly drawn upwards (Figure 1.7) while rotating the crucible in the opposite direction. The liquid silicon thus solidifies into a continuous crystal extending from the initial seed. At the beginning of the process, temperature and pulling speed are adjusted to "neck" the crystal diameter to 5 mm, in order to eliminate the dislocations generated by the seed/melt contact shock.

Once this neck reaches a few centimeters in height, the crystal diameter is enlarged to form a cone until it reaches the target diameter value. Typical diameter for PV samples is 210 mm, although it is rapidly increasing towards higher values to meet the requirements for larger wafers. The cylindrical part of the body with constant diameter is then grown by controlling the pulling rate and the melt temperature. Near the end of the growth process, the diameter is again gradually reduced to form an end-cone and minimize thermal shock. The single crystal can then be separated from the melt without generation of dislocations [105].

<sup>&</sup>lt;sup>7</sup> For PV applications, orientation is {100} to facilitate the surface texturing (detailed in Chapter 3) of the wafers.

The cylindrical ingots need to be reshaped into square or pseudo-square bricks in order to be compatible with the solar cell shape. Although this "lost material" can be re-used as raw material for other processes, it remains one of the main disadvantages of the Cz process, together with its relatively high cost.

Impurities in Cz silicon can be classified into two categories: dopants and contaminants. Doping elements are voluntarily introduced to improve the properties (mainly electrical) of the silicon crystal, while contaminants are unintentionally incorporated during the growth. The most abundant non-doping impurity in Cz silicon is unquestionably oxygen, which is incorporated in the melt from the corrosion of the quartz crucible walls during the growth [106]. Its inherent presence, with concentrations in the order of 10<sup>18</sup> atoms/cm<sup>3</sup>, can generate numerous types of defects: oxide precipitates [107,108], thermal donors (small chains formed by aggregation of a few atoms of Si and Oi [109,110]) and so-called light-induced degradation (LID) defects which are activated after crystallization under carrier injection, either provided by illumination or by current [111]. These degradation mechanisms are mainly related to Boron-Oxygen (B-O) complexes [112] or interstitial copper contamination [113]. To a lesser extent, carbon impurities coming from the graphite elements of the furnace can also deteriorate ingot quality, for example by entering into reaction with SiO vapor to form SiC precipitates and carbon monoxide gas.

### 3.1.2. Directional solidification process

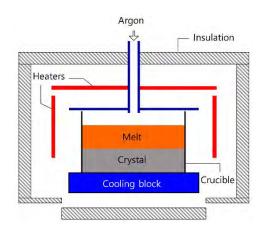

The directional solidification method is a lower cost alternative for the growth of solar silicon, as it allows to manufacture square ingots of more than 1.25 meter wide (so called G8 ingot) from which 8 × 8 bricks of 156 mm in section can be obtained. This process uses solar grade polysilicon (6N), which is placed together with the doping material in a square-shaped and  $Si_3N_4$ -coated fused silica crucible [114]. Once the feedstock is completely melted, a vertical temperature gradient is applied and crystallization occurs as the solid / liquid interface moves from the bottom to the top of the crucible with a growth rate of 1 to 2 cm/h. This procedure allows purifying the silicon material, because the impurities from the releasing coating and crucible (mainly metallic) are more soluble in the liquid phase and segregate towards the top of the ingot [115]. A standard directional solidification system is illustrated in Figure 1.8.

There are many variants regarding the furnace design and the cooling system [116], but the system is usually composed of an insulating chamber with heaters on the sides and top. Crystallization is carried out by extracting the heat through the crucible bottom with the help of a liquid-cooled heat exchanger.

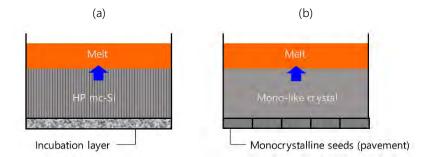

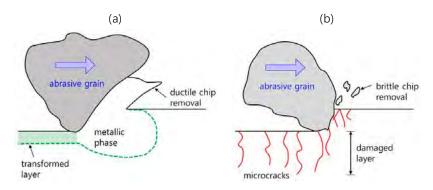

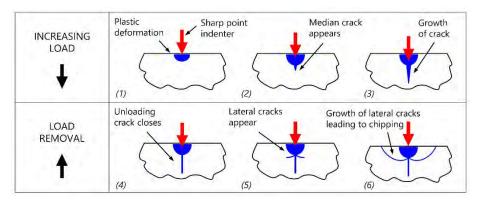

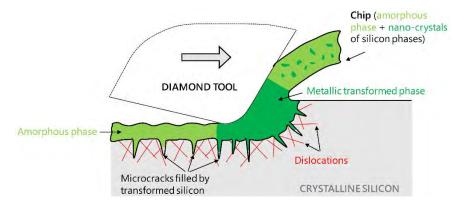

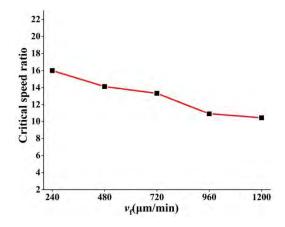

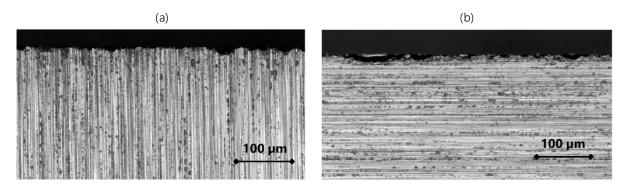

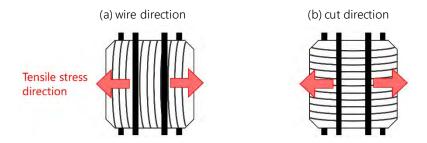

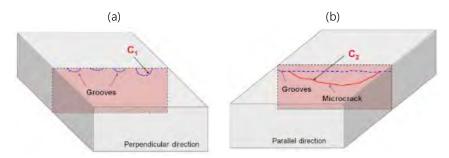

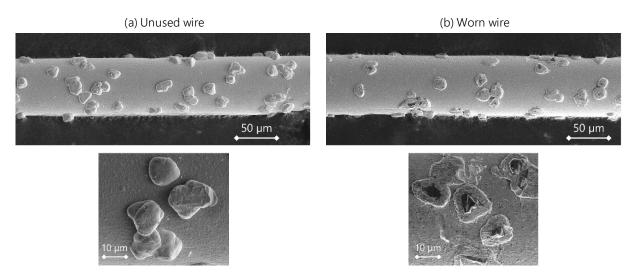

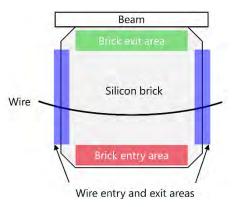

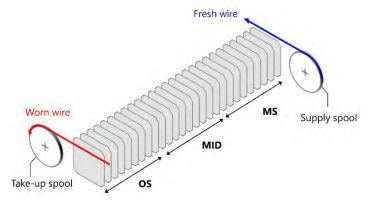

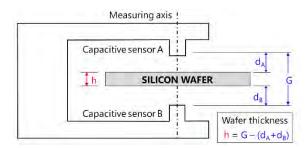

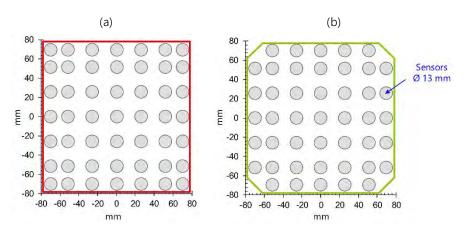

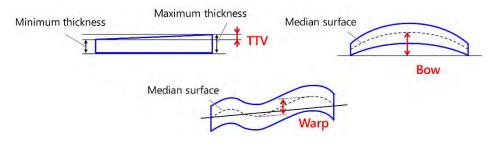

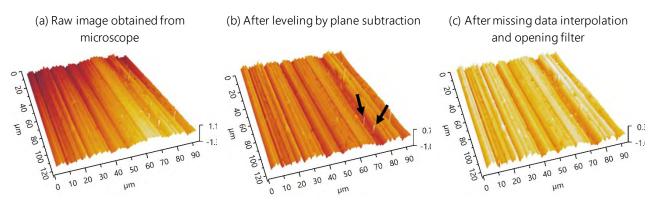

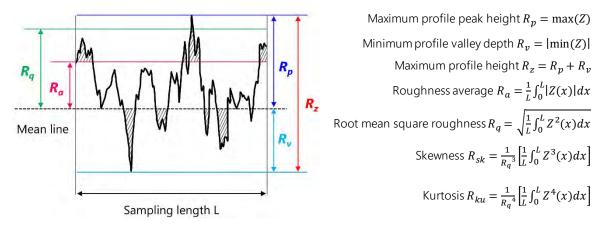

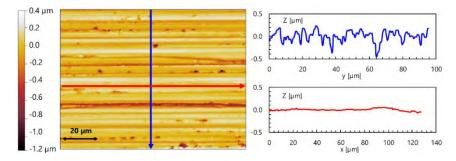

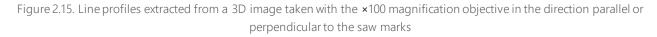

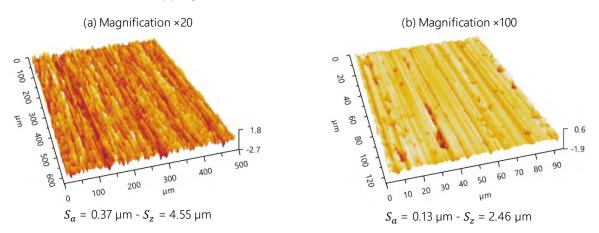

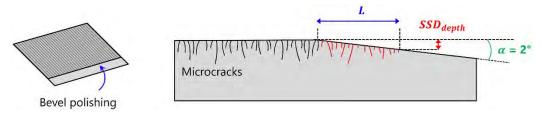

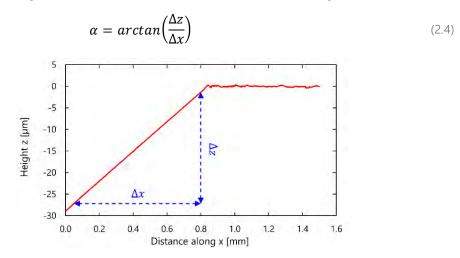

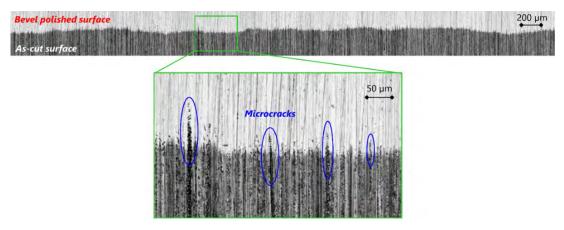

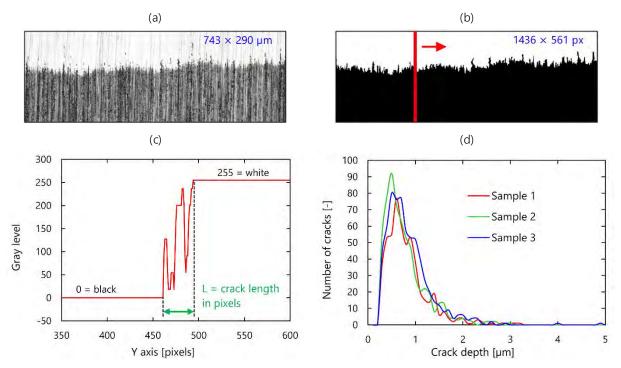

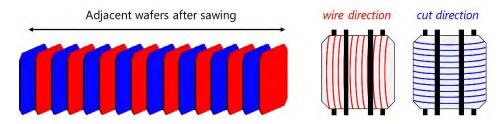

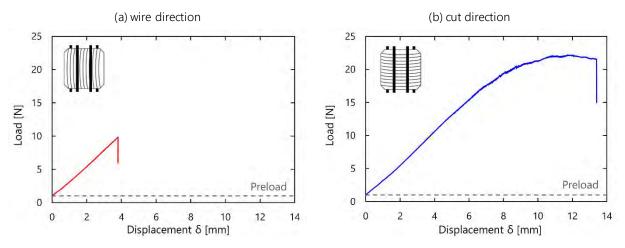

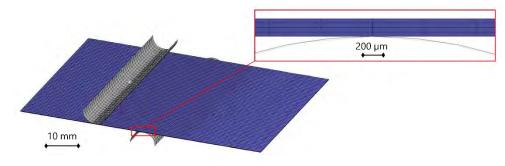

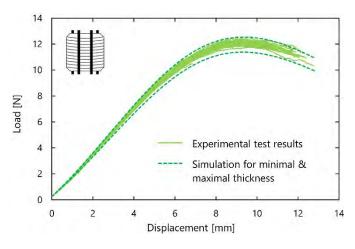

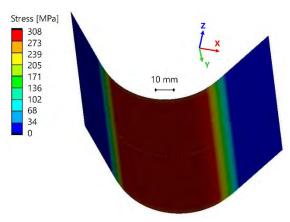

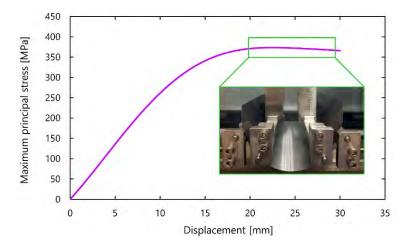

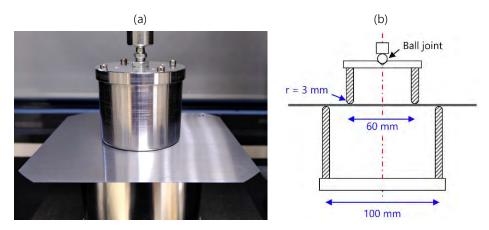

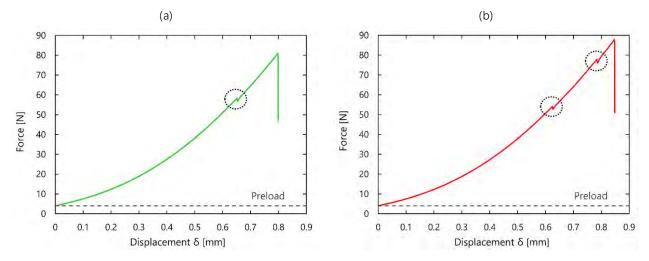

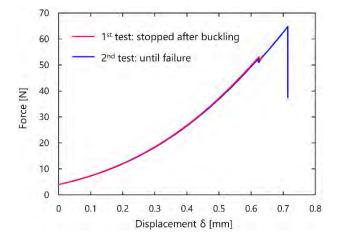

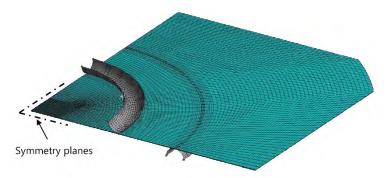

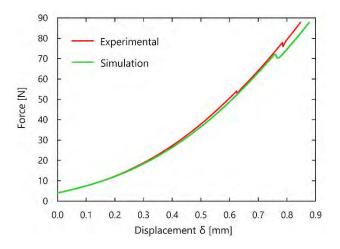

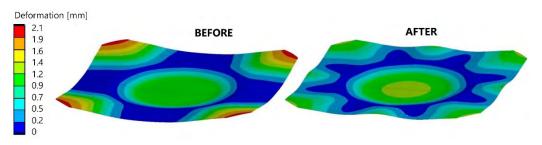

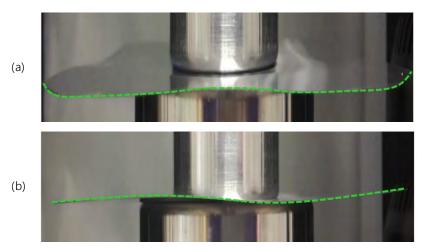

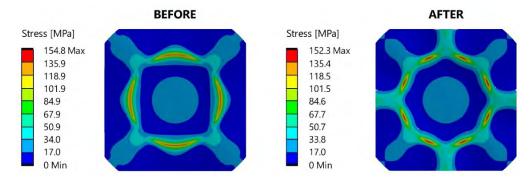

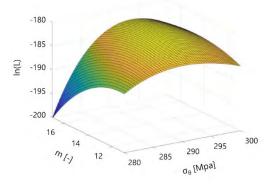

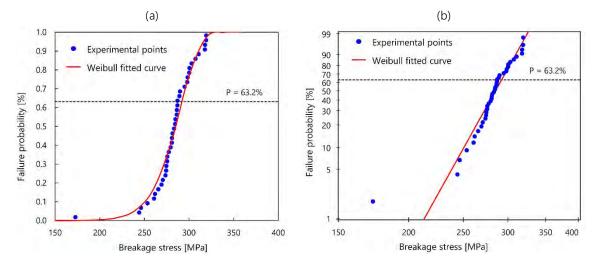

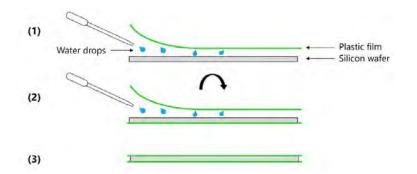

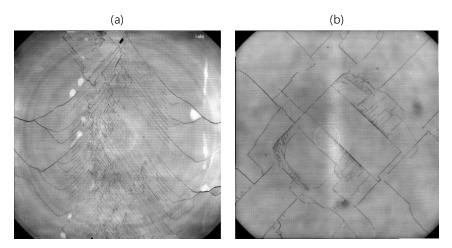

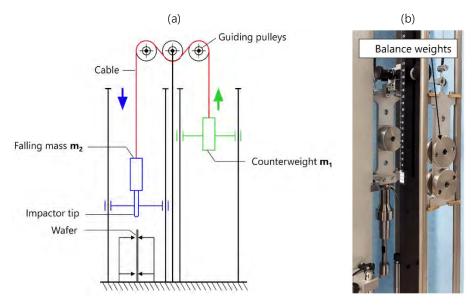

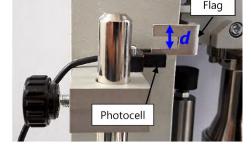

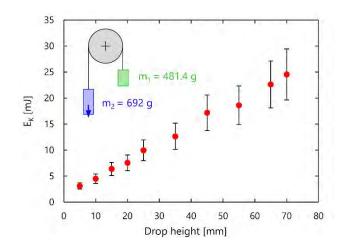

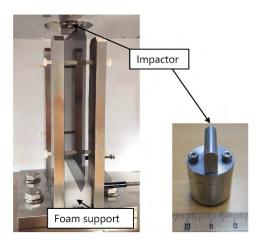

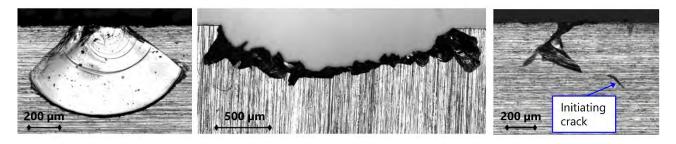

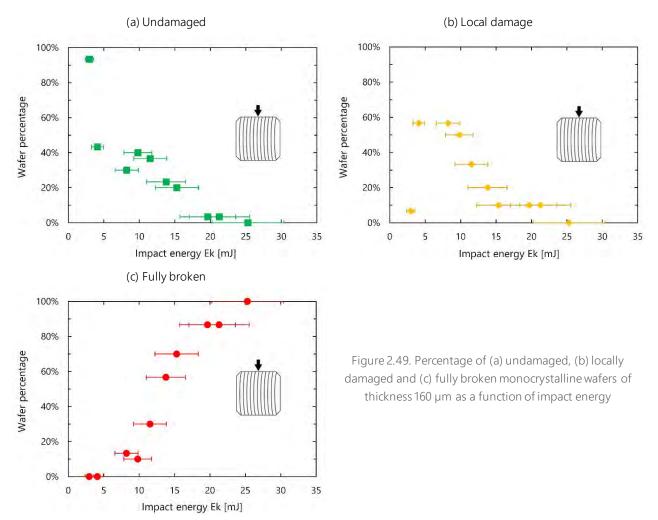

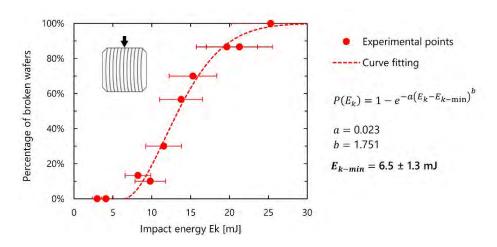

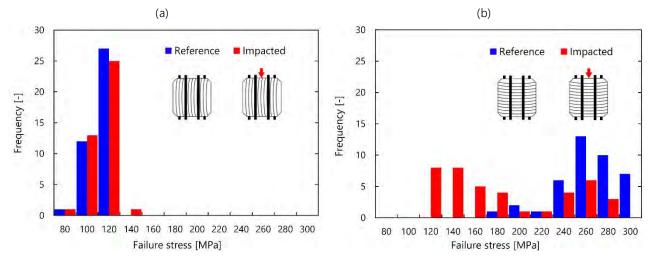

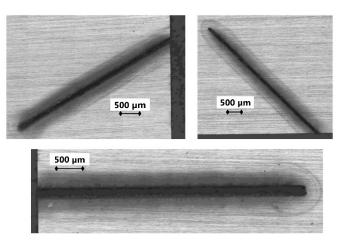

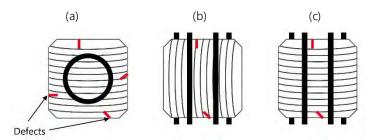

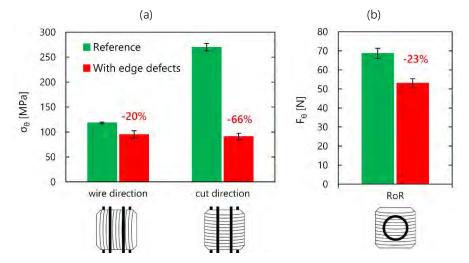

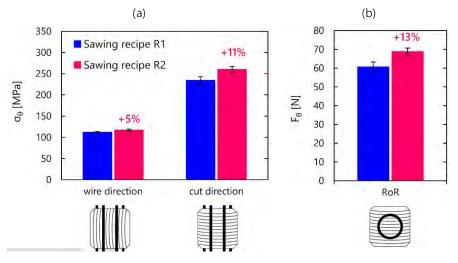

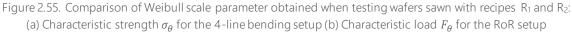

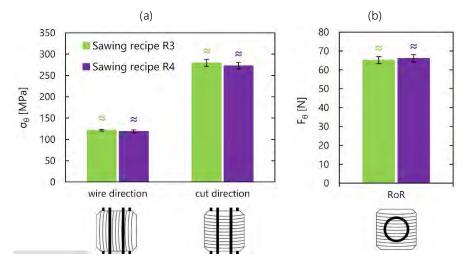

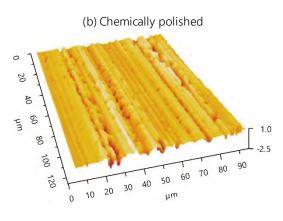

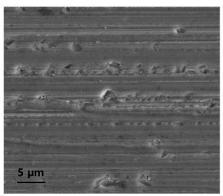

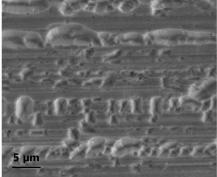

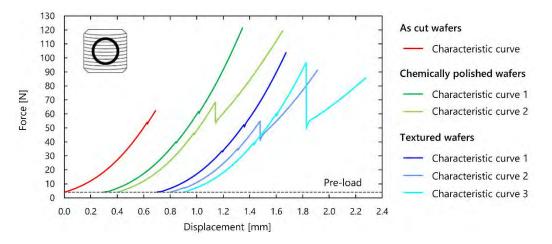

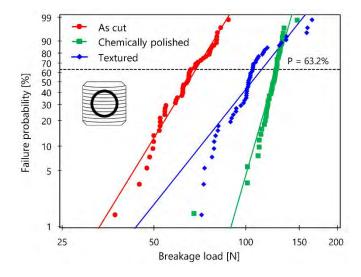

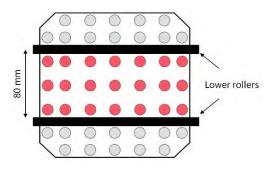

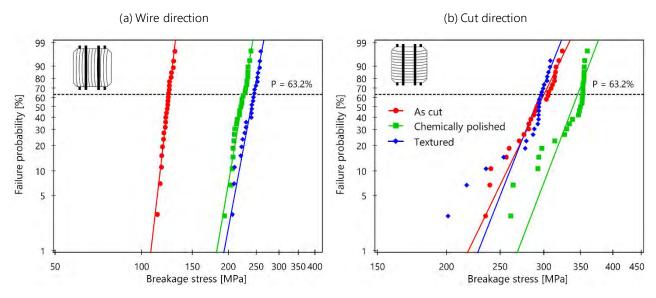

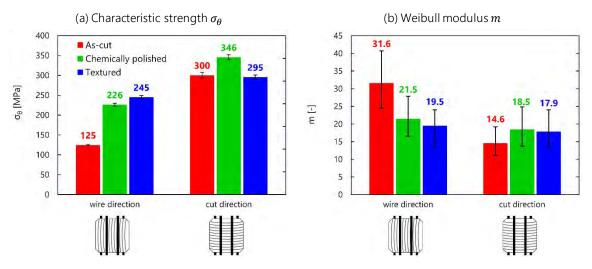

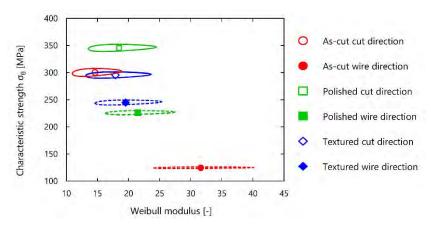

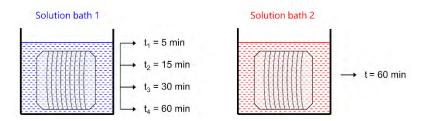

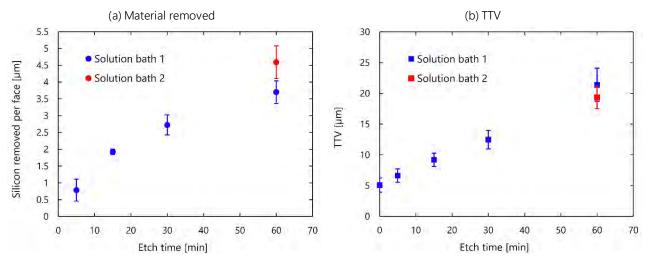

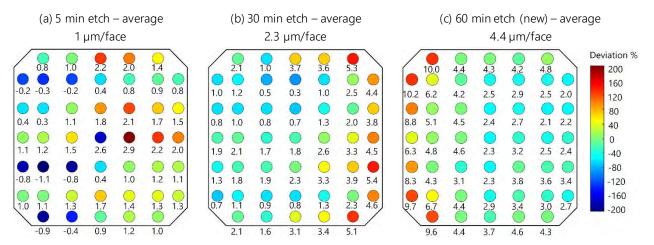

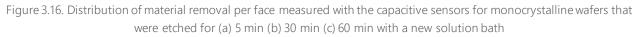

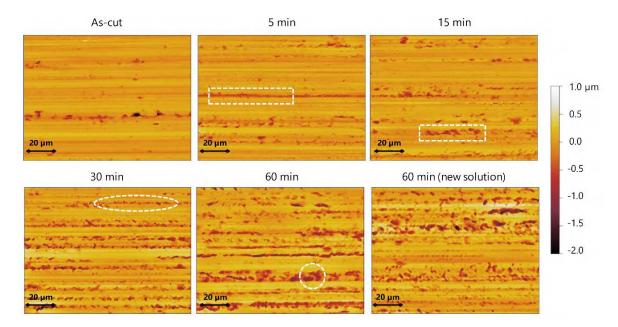

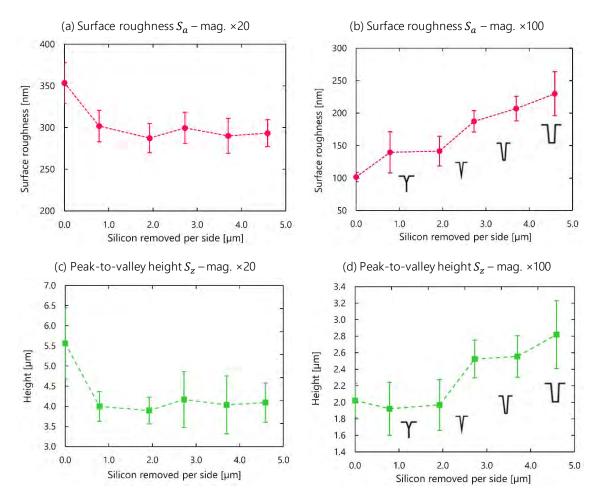

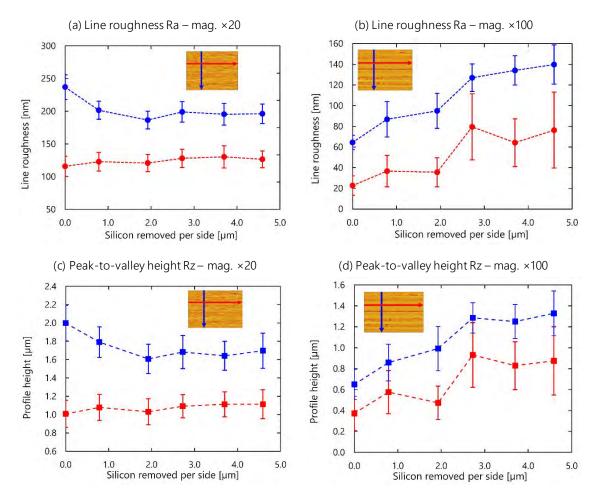

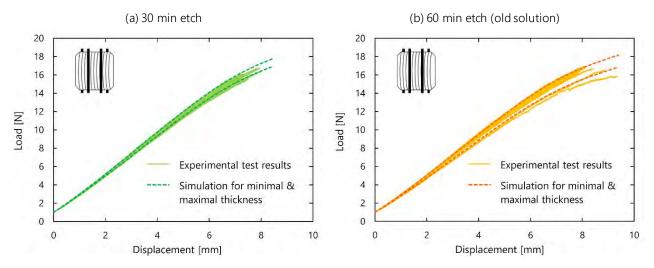

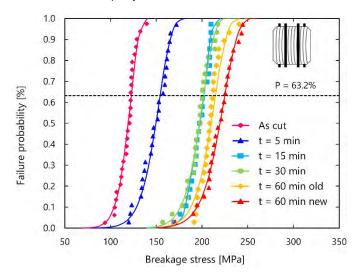

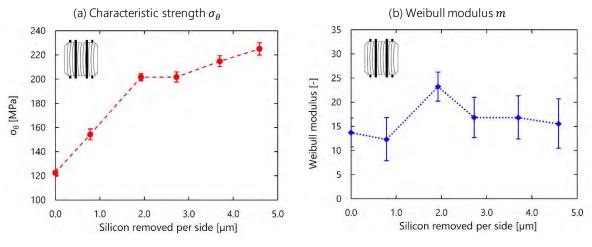

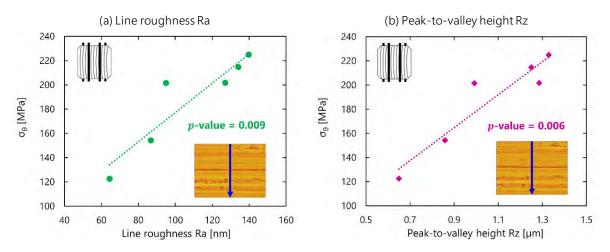

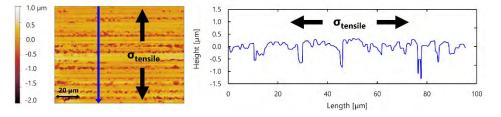

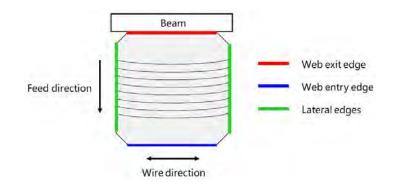

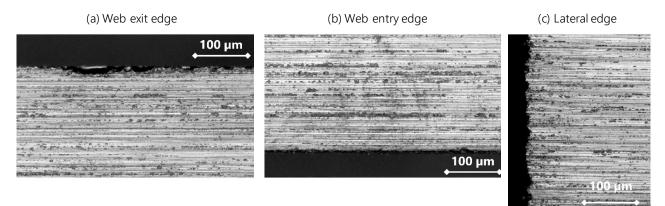

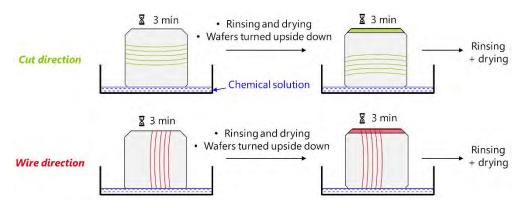

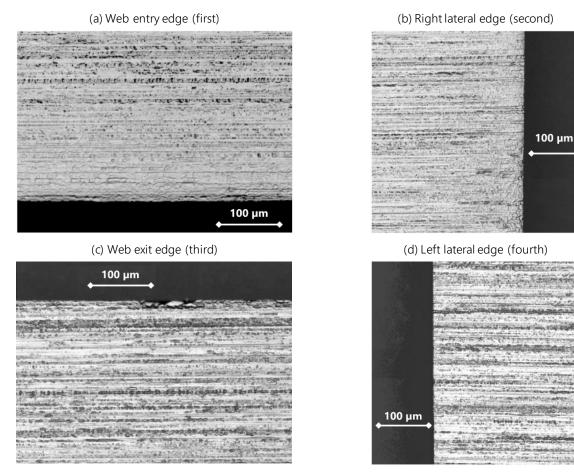

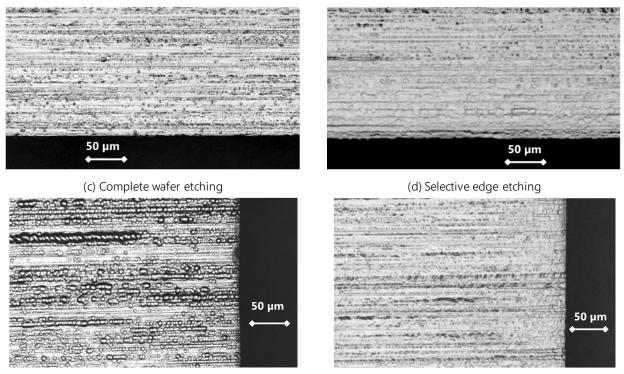

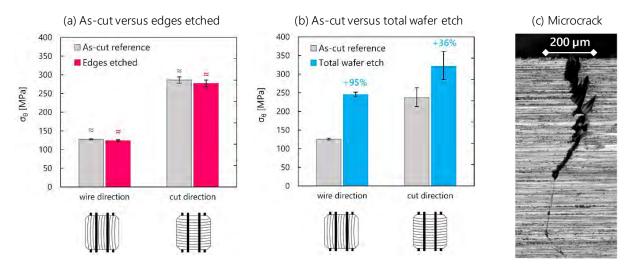

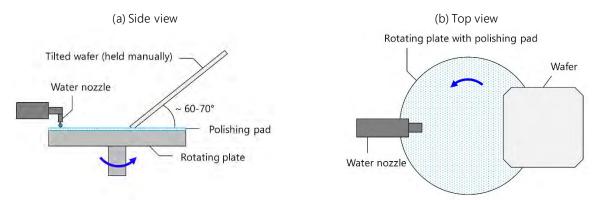

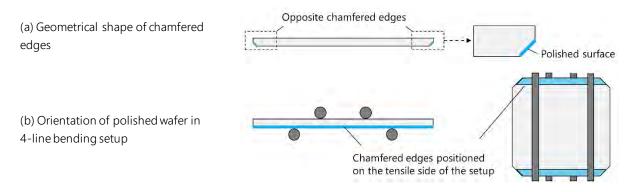

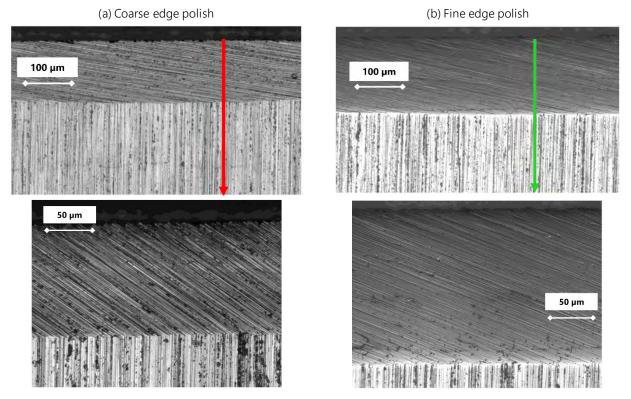

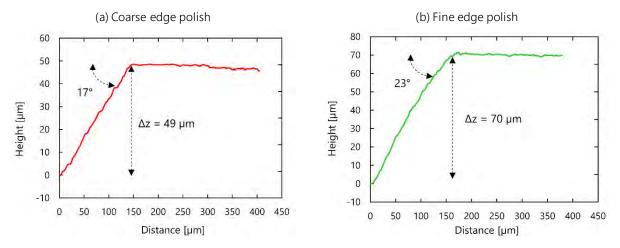

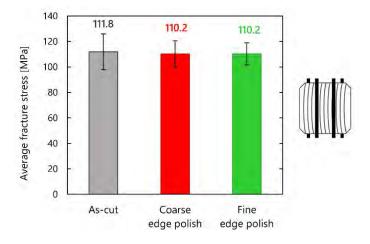

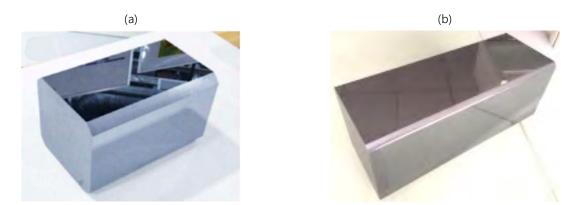

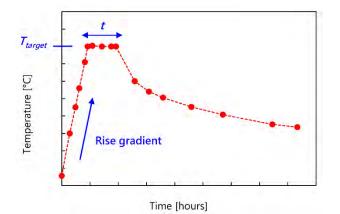

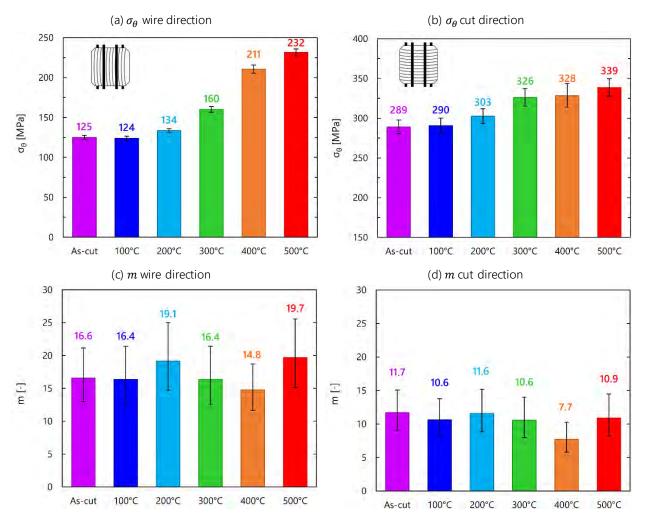

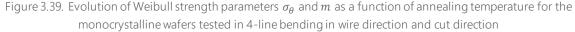

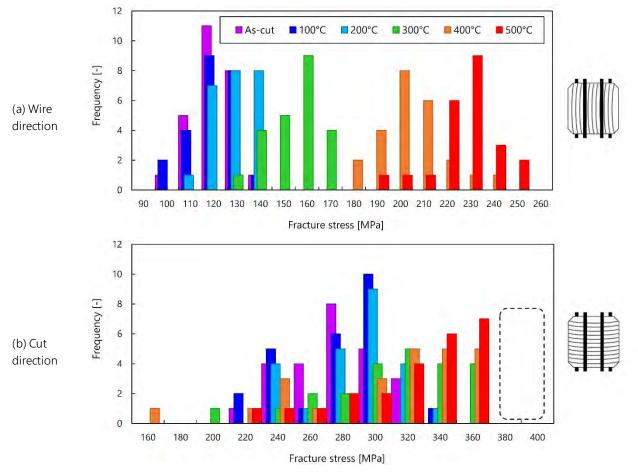

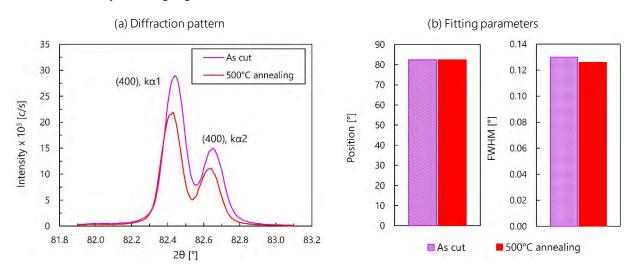

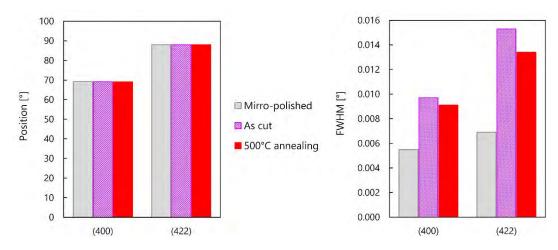

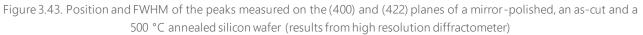

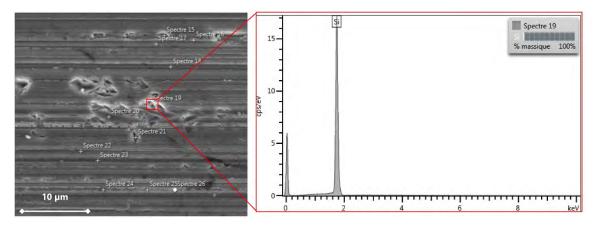

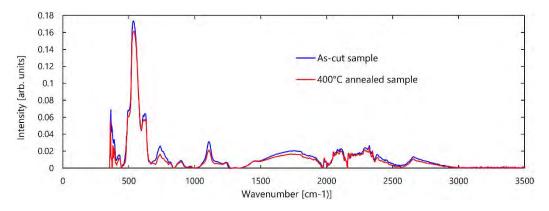

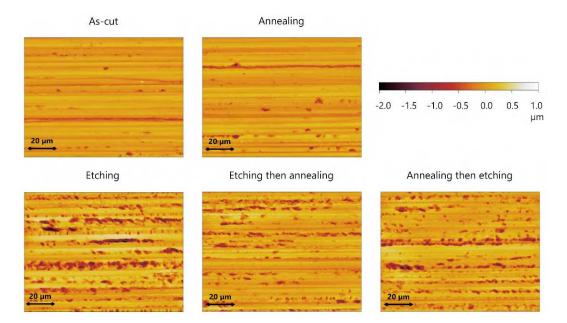

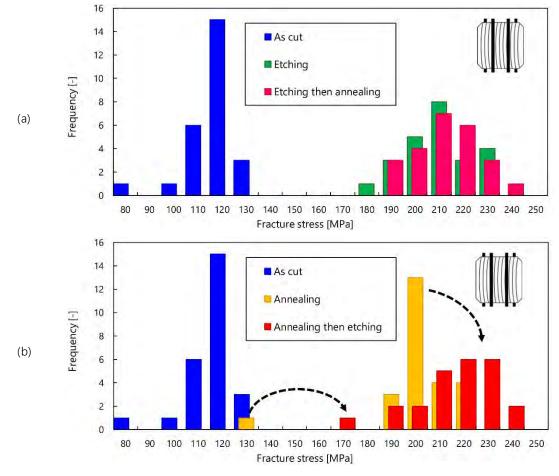

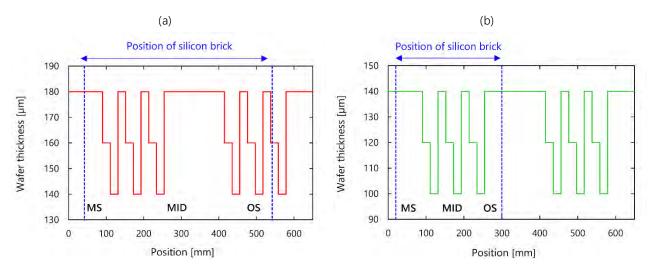

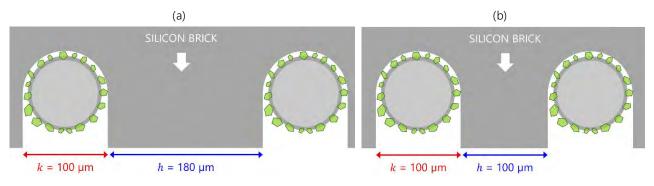

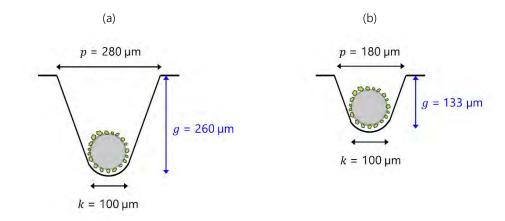

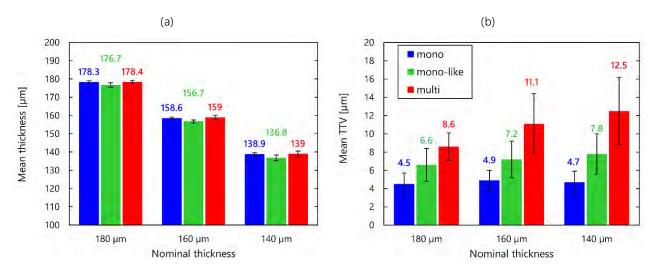

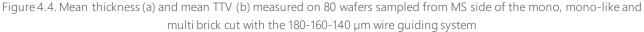

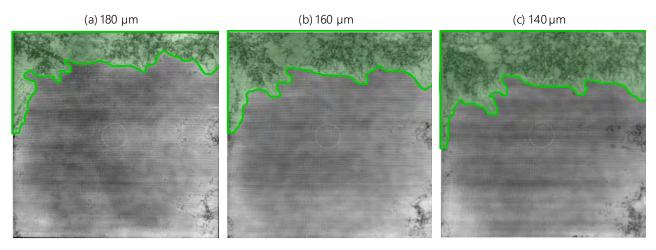

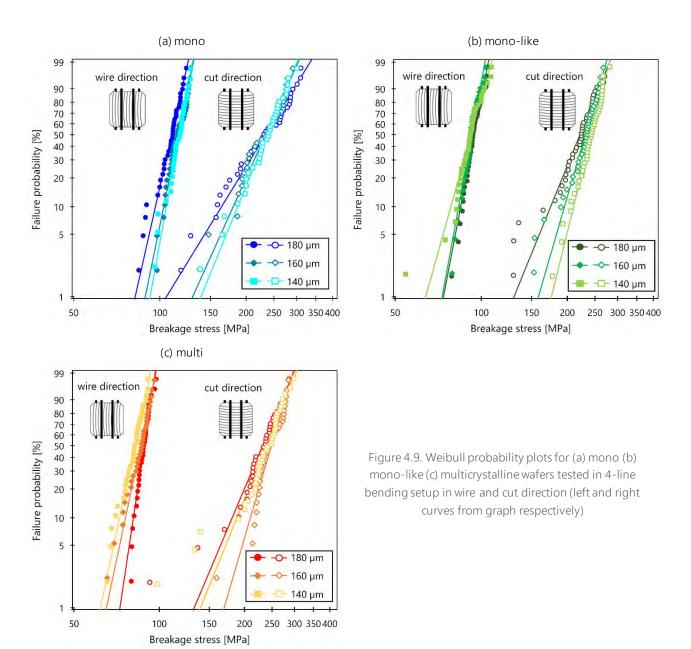

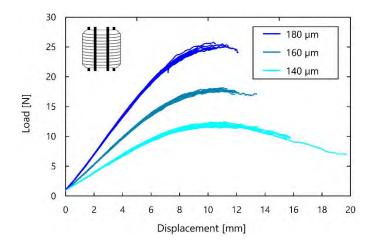

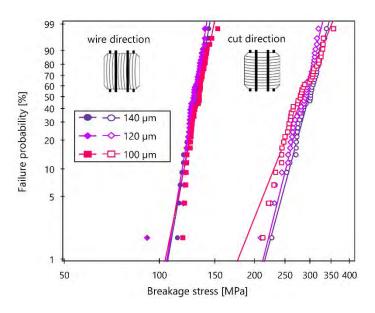

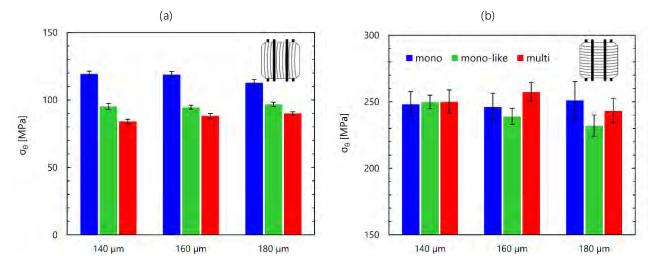

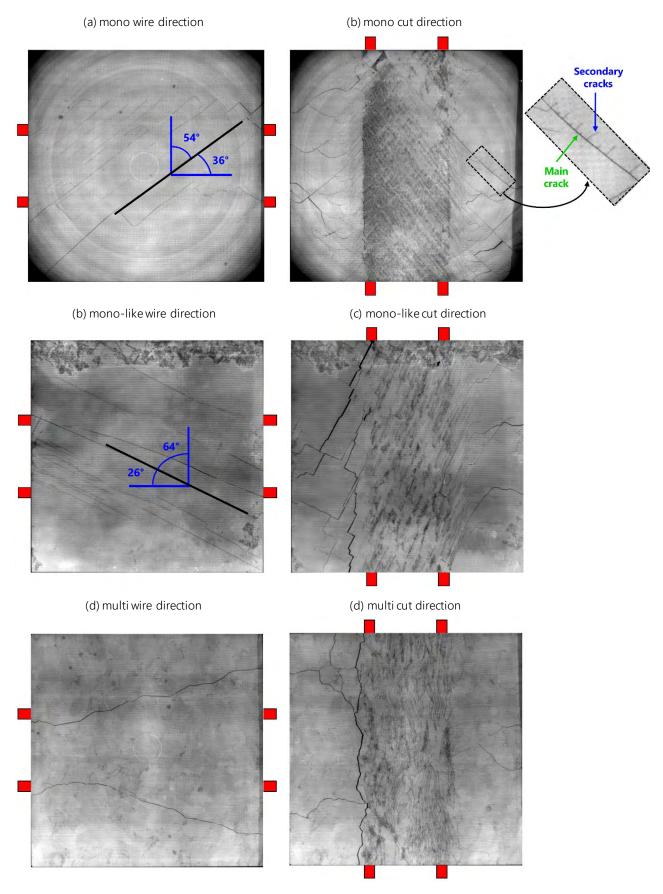

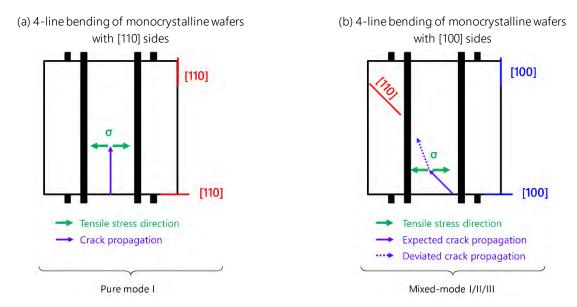

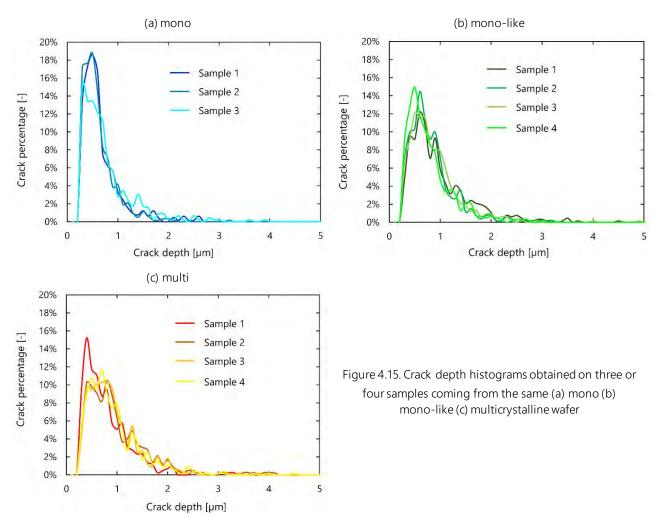

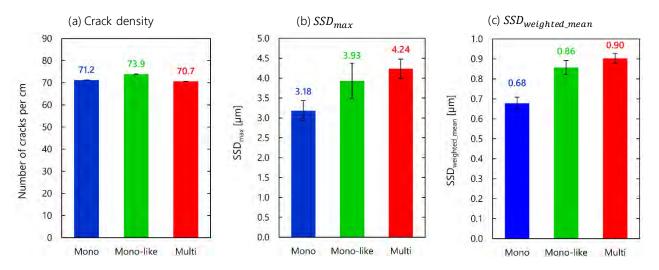

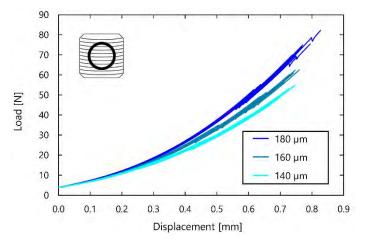

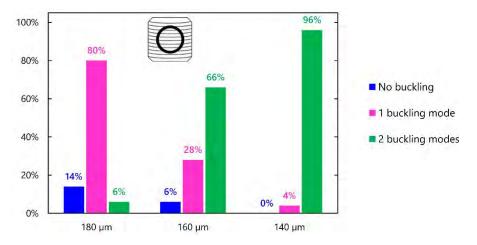

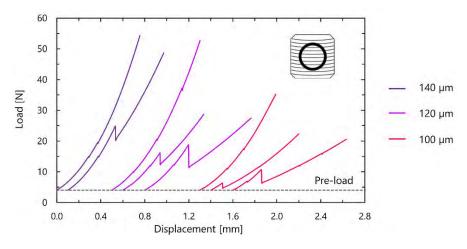

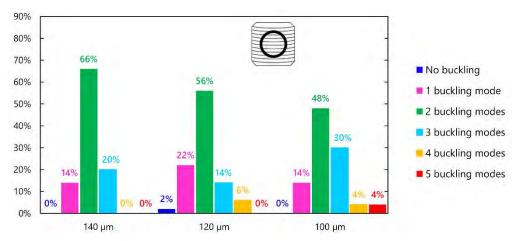

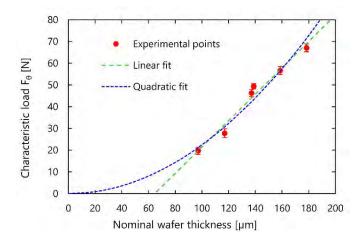

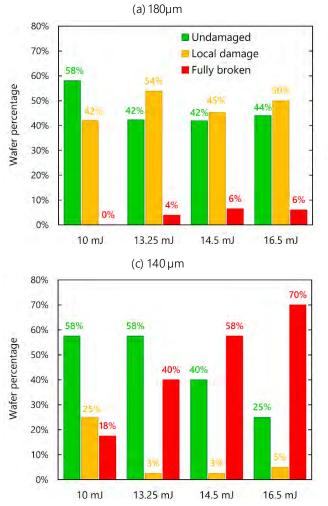

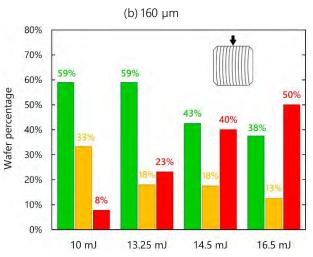

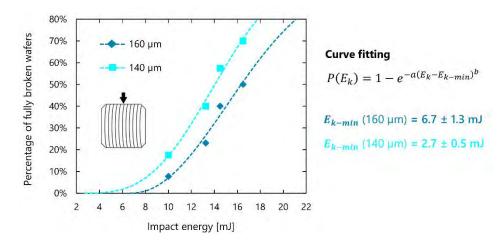

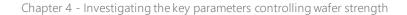

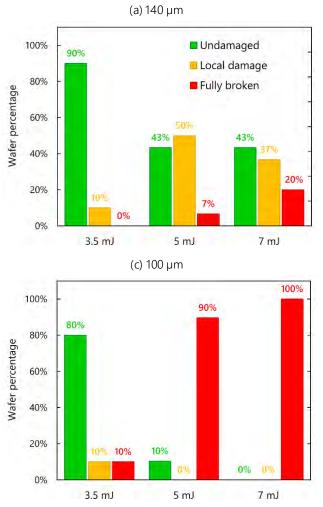

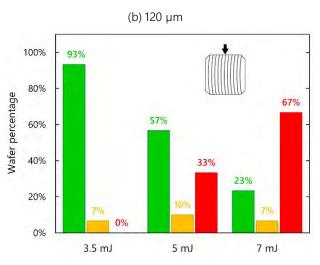

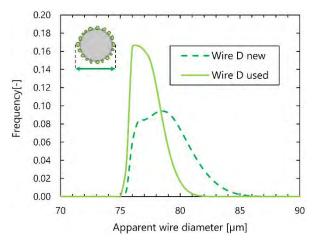

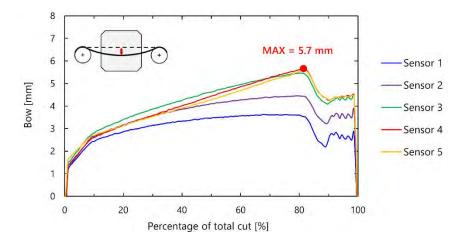

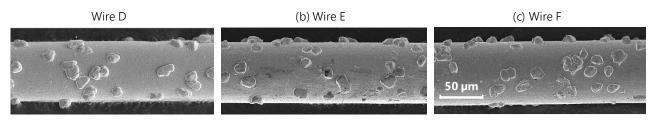

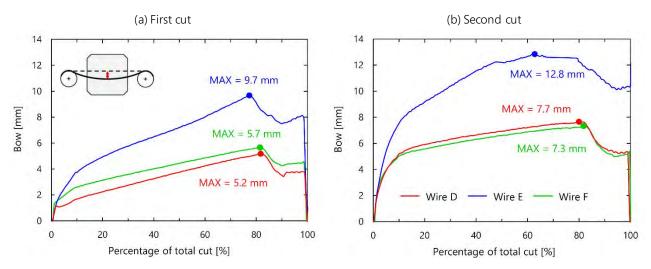

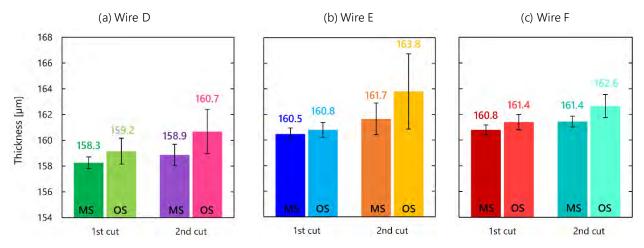

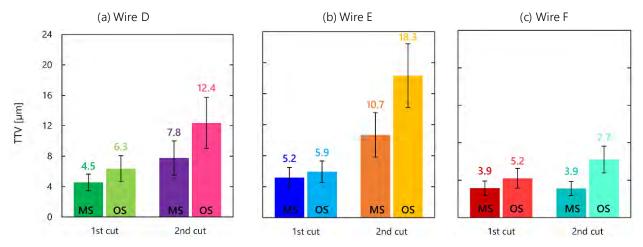

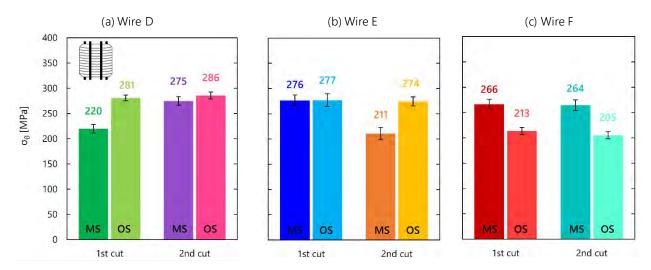

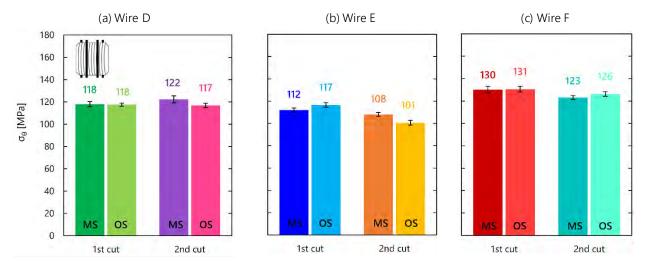

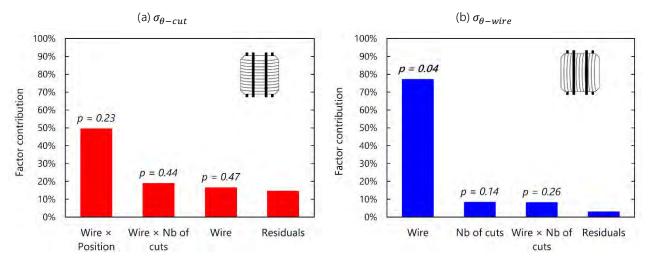

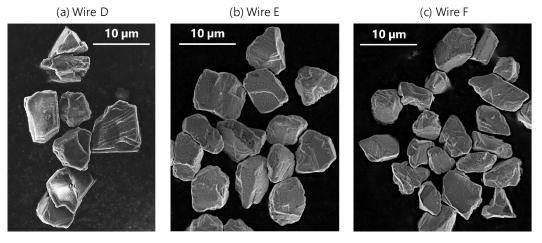

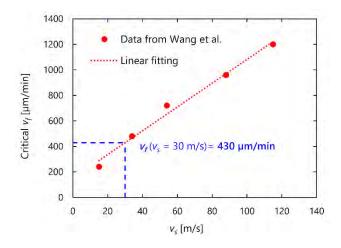

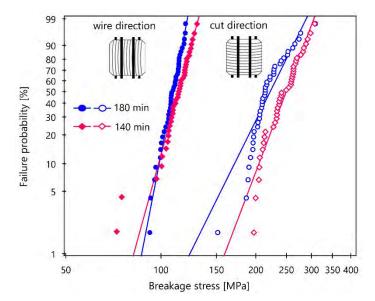

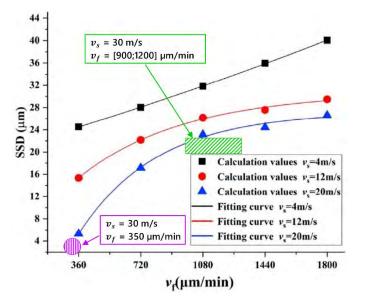

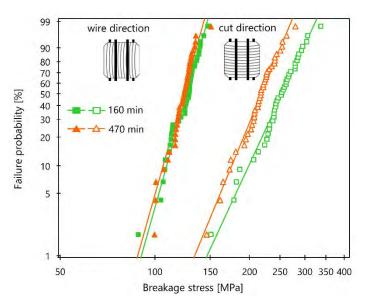

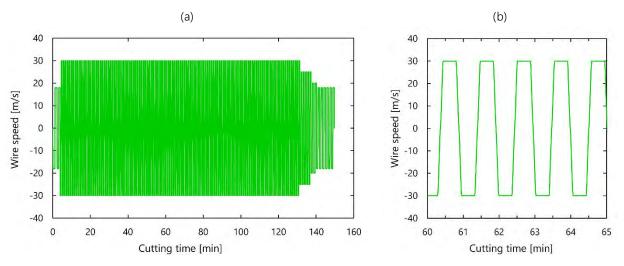

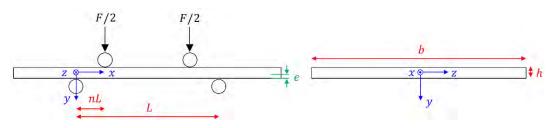

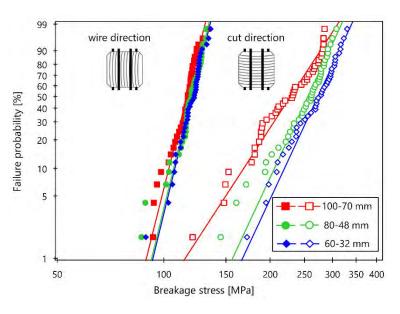

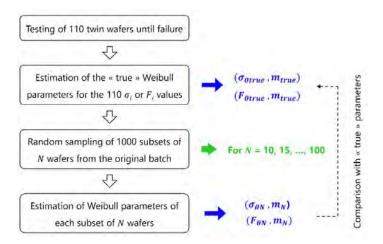

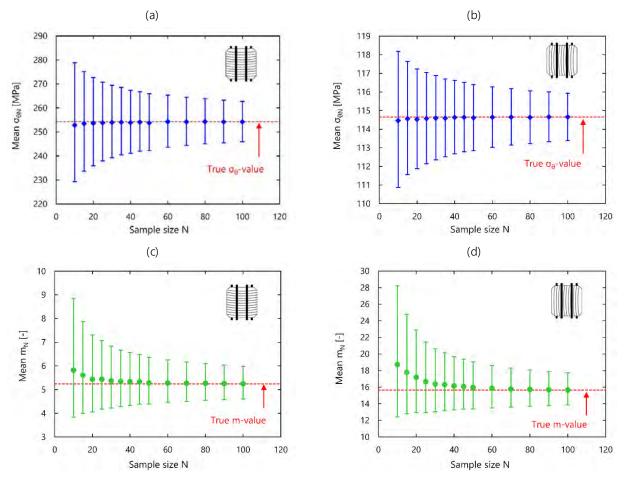

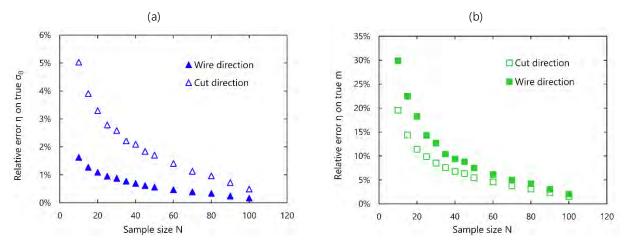

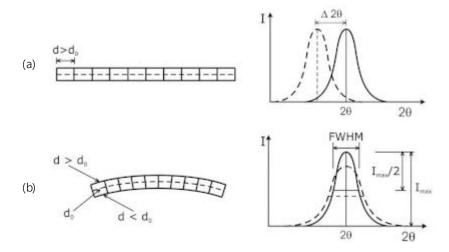

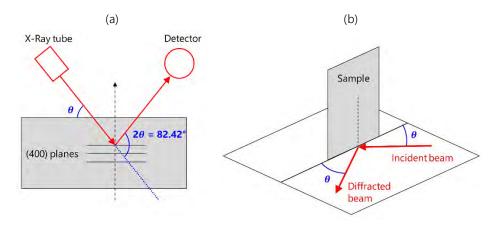

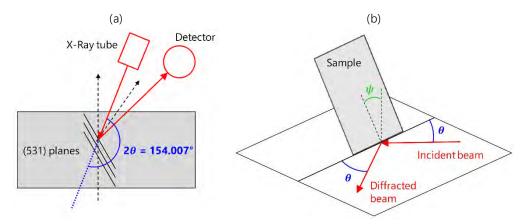

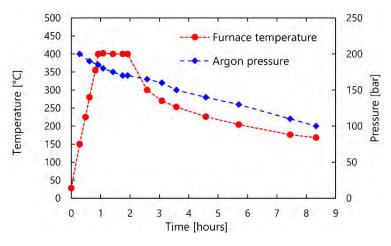

Figure 1.8. Schematic description of a directional solidification system